PDP-9 Maintenance Manual

# RF09/RS09 DECDISK SYSTEM

Volume I

## RF09/RS09 DECDISK SYSTEM MAINTENANCE MANUAL VOLUME 1

Copyright © 1970, by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

COMPUTR LAB

## CONTENTS

| CHAPTER 1   DECDISK SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                       | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|------|

| 1.1         Introduction         1-1           1.1.1         DECdisk System Description         1-1           1.1.2         Storage of Digital Data on Fixed-Head Rotating Disks         1-1           1.1.3         Storage of Data in a Serial Format         1-3           1.1.4         Random Accessing of Data         1-3           1.1.5         Data Accessing at Selectable Speeds         1-3           1.1.6         Data Protection from Over-Writing         1-3           1.2         DECdisk Operation         1-3           1.2.1         Disk Surface Recording Format         1-3           1.2.2         DECdisk Architecture         1-6           1.2.2.1         The Control Section         1-6           1.2.2.2.3         Maintenance Section         1-10           1.2.2.2.3         Maintenance Section         1-16           1.3.1         Transfer Rate Selection         1-16           1.3.2         Disk Address Selection Jacks         1-19           1.3.3         Write Lockout Switches         1-19           1.4         The Operator's Indicators         1-21           1.5         Programming Examples         1-22           1.6         Programming With the ADS Register         1-25 <tr< th=""><th></th><th></th><th></th></tr<> |           |                                       |      |

| 1.1.1       DECdisk System Description       1-1         1.1.2       Storage of Digital Data on Fixed-Head Rotating Disks       1-1         1.1.3       Storage of Data in a Serial Format       1-3         1.1.4       Random Accessing at Selectable Speeds       1-3         1.1.5       Data Accessing at Selectable Speeds       1-3         1.1.6       Data Protection from Over-Writing       1-3         1.2.1       Disc Surface Recording Format       1-3         1.2.1       Disk Surface Recording Format       1-3         1.2.2.1       The Control Section       1-6         1.2.2.2.1       The Control Section       1-6         1.2.2.2.3       Maintenance Section       1-10         1.2.2.3       Maintenance Section       1-16         1.3.1       Transfer Rate Selection Jacks       1-19         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.9       Summary of DECdis                                                                  | CHAPTER 1 | DECDISK SYSTEM                        |      |

| 1.1.2     Storage of Digital Data on Fixed-Head Rotating Disks     1.1       1.1.3     Storage of Data in a Serial Format     1.3       1.1.4     Random Accessing of Data     1.3       1.1.5     Data Accessing at Selectable Speeds     1.3       1.1.6     Data Protection from Over-Writing     1.3       1.2     DECdisk Operation     1.3       1.2.1     Disk Surface Recording Format     1.3       1.2.2     DECdisk Architecture     1.6       1.2.2.1     The Control Section     1.6       1.2.2.2     The Data Transfer Section     1.10       1.2.2.3     Maintenance Section     1.15       1.3     The Operator's Controls     1.16       1.3.1     Transfer Rate Selection     1.16       1.3.2     Disk Address Selection Jacks     1.19       1.3.3     Write Lockout Switches     1.19       1.4     The Operator's Indicators     1.21       1.5     Programming Examples     1.22       1.6     Programming With the ADS Register     1.25       1.7     Programming Multiple Disk Systems     1.27       1.8     Using DECdisk in a System     1.27       1.9     Summary of DECdisk Characteristics     1.29       2.1     Introduction     2.1       2.1.1                                                                                                | 1.1       | Introduction                          | 1-1  |

| 1.1.2     Storage of Digital Data on Fixed-Head Rotating Disks     1.1       1.1.3     Storage of Data in a Serial Format     1.3       1.1.4     Random Accessing of Data     1.3       1.1.5     Data Accessing at Selectable Speeds     1.3       1.1.6     Data Protection from Over-Writing     1.3       1.2     DECdisk Operation     1.3       1.2.1     Disk Surface Recording Format     1.3       1.2.2     DECdisk Architecture     1.6       1.2.2.1     The Control Section     1.6       1.2.2.2     The Data Transfer Section     1.10       1.2.2.3     Maintenance Section     1.15       1.3     The Operator's Controls     1.16       1.3.1     Transfer Rate Selection     1.16       1.3.2     Disk Address Selection Jacks     1.19       1.3.3     Write Lockout Switches     1.19       1.4     The Operator's Indicators     1.21       1.5     Programming Examples     1.22       1.6     Programming With the ADS Register     1.25       1.7     Programming Multiple Disk Systems     1.27       1.8     Using DECdisk in a System     1.27       1.9     Summary of DECdisk Characteristics     1.29       2.1     Introduction     2.1       2.1.1                                                                                                | 1.1.1     | DECdisk System Description            | 1-1  |

| 1.1.3       Storage of Data in a Serial Format       1.3         1.1.4       Random Accessing of Data       1.3         1.1.5       Data Accessing at Selectable Speeds       1.3         1.1.6       Data Protection from Over-Writing       1.3         1.2       DECdisk Operation       1.3         1.2.1       Disk Surface Recording Format       1.6         1.2.1       DECdisk Architecture       1.6         1.2.2.1       The Control Section       1.6         1.2.2.2       The Data Transfer Section       1.10         1.2.2.3       Maintenance Section       1.16         1.3       The Operator's Controls       1.16         1.3.1       Transfer Rate Selection       1.16         1.3.2       Disk Address Selection Jacks       1.19         1.3.3       Write Lockout Switches       1.19         1.4       The Operator's Indicators       1.21         1.5       Programming Examples       1.22         1.6       Programming With the ADS Register       1.25         1.7       Programming Multiple Disk Systems       1.27         1.8       Using DECdisk Characteristics       2.1         2.1       Introduction       2.1         2.1.2                                                                                                            | 1.1.2     |                                       | 1-1  |

| 1.1.5       Data Accessing at Selectable Speeds       1.3         1.1.6       Data Protection from Over-Writing       1.3         1.2       DECdisk Operation       1.3         1.2.1       Disk Surface Recording Format       1.3         1.2.2       DECdisk Architecture       1-6         1.2.2.1       The Control Section       1-6         1.2.2.2       The Data Transfer Section       1-10         1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3                                                                                                            | 1.1.3     |                                       | 1-3  |

| 1.1.6         Data Protection from Over-Writing         1.3           1.2         DECdisk Operation         1.3           1.2.1         Disk Surface Recording Format         1.3           1.2.2         DECdisk Architecture         1-6           1.2.2.1         The Control Section         1-6           1.2.2.2         The Data Transfer Section         1-10           1.2.2.3         Maintenance Section         1-15           1.3         The Operator's Controls         1-16           1.3.1         Transfer Rate Selection         1-16           1.3.2         Disk Address Selection Jacks         1-19           1.3.3         Write Lockout Switches         1-19           1.4         The Operator's Indicators         1-21           1.5         Programming Examples         1-22           1.6         Programming Examples         1-25           1.6         Programming Multiple Disk Systems         1-27           1.8         Using DECdisk in a System         1-27           1.9         Summary of DECdisk Characteristics         2-2           2.1         Introduction         2-1           2.1.1         Types of Modules         2-1           2.1.2         Measurement Definit                                                          | 1.1.4     | Random Accessing of Data              | 1-3  |

| 1.2       DECdisk Operation       1.3         1.2.1       Disk Surface Recording Format       1.3         1.2.2       DECdisk Architecture       1-6         1.2.2.1       The Control Section       1-6         1.2.2.2       The Data Transfer Section       1-10         1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection Jacks       1-19         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       2-2         CHAPTER 2       DECDISK MODULES         2.1       Types of Modules       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2 <td>1.1.5</td> <td>Data Accessing at Selectable Speeds</td> <td>1-3</td>                                                  | 1.1.5     | Data Accessing at Selectable Speeds   | 1-3  |

| 1.2.1       Disk Surface Recording Format       1-3         1.2.2       DECdisk Architecture       1-6         1.2.2.1       The Control Section       1-6         1.2.2.2       The Data Transfer Section       1-10         1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming Examples       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3                                                                                                                                                | 1.1.6     | Data Protection from Over-Writing     | 1-3  |

| 1.2.2.1       DECdisk Architecture       1-6         1.2.2.1       The Control Section       1-6         1.2.2.2       The Data Transfer Section       1-10         1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection Jacks       1-19         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2         DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       2-3       2-3         2.3       G285 Series Switch       2                                                                                                                                                       | 1.2       | DECdisk Operation                     | 1-3  |

| 1.2.2.1       DECdisk Architecture       1-6         1.2.2.1       The Control Section       1-6         1.2.2.2       The Data Transfer Section       1-10         1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection Jacks       1-19         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2         DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       2-3       2-3         2.3       G285 Series Switch       2                                                                                                                                                       | 1.2.1     | Disk Surface Recording Format         | 1-3  |

| 1.2.2.2       The Data Transfer Section       1-10         1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.1.3       Loading       2-2         2.2.1       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5 <td>1.2.2</td> <td></td> <td>1-6</td>                                                                                                        | 1.2.2     |                                       | 1-6  |

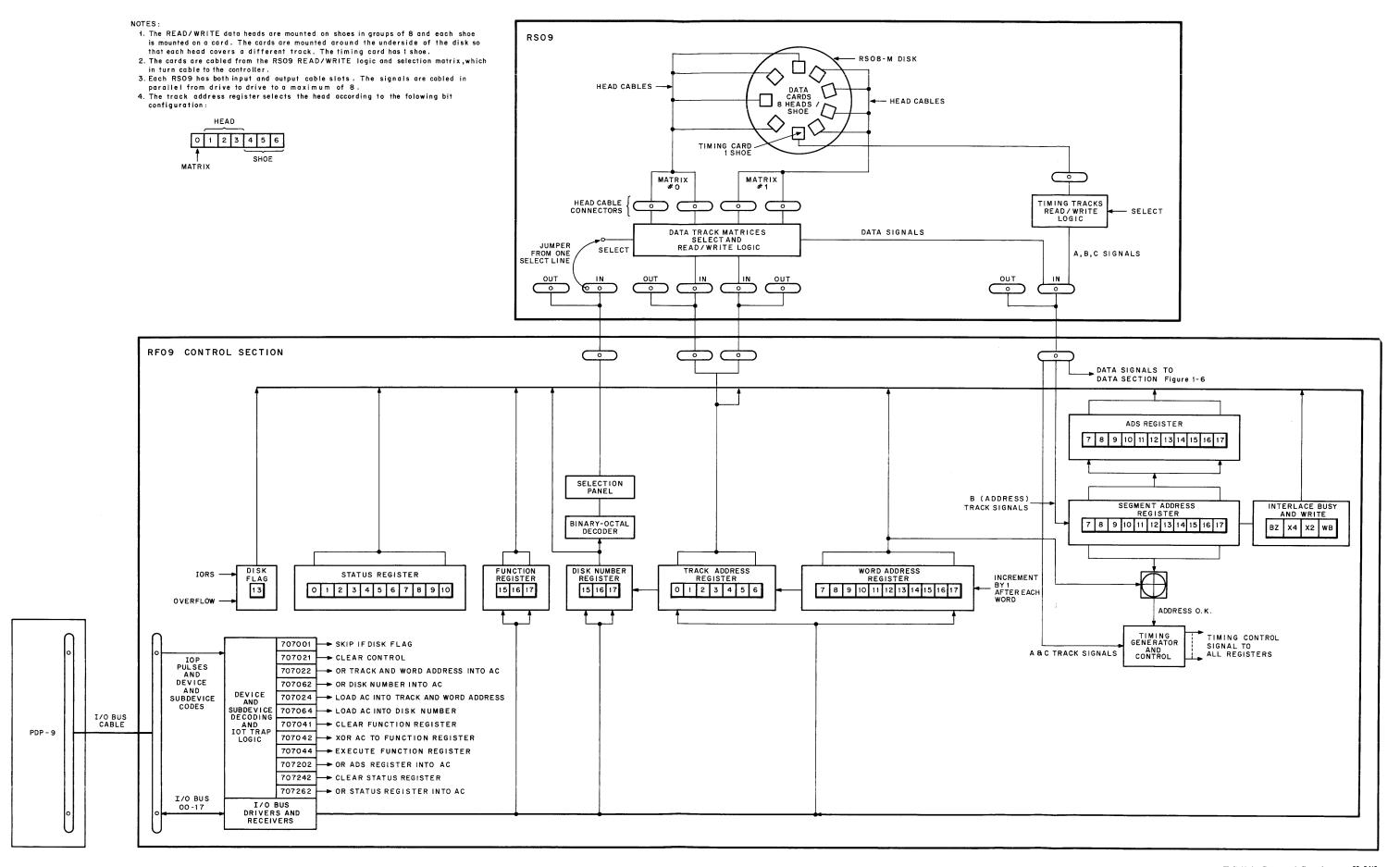

| 1.2.2.3       Maintenance Section       1.15         1.3       The Operator's Controls       1.16         1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming Wultiple Disk Systems       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2         DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix <t< td=""><td>1.2.2.1</td><td>The Control Section</td><td>1-6</td></t<>                                                                                    | 1.2.2.1   | The Control Section                   | 1-6  |

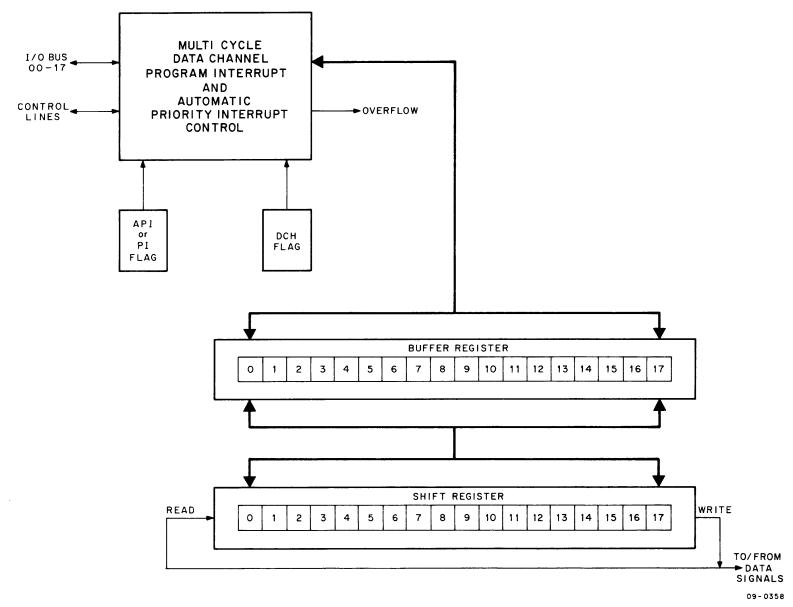

| 1.2.2.3       Maintenance Section       1-15         1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2         DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Hip-Flop       2-13         2.6       G681 B Track Matrix <td< td=""><td>1.2.2.2</td><td>The Data Transfer Section</td><td>_</td></td<>                                                                               | 1.2.2.2   | The Data Transfer Section             | _    |

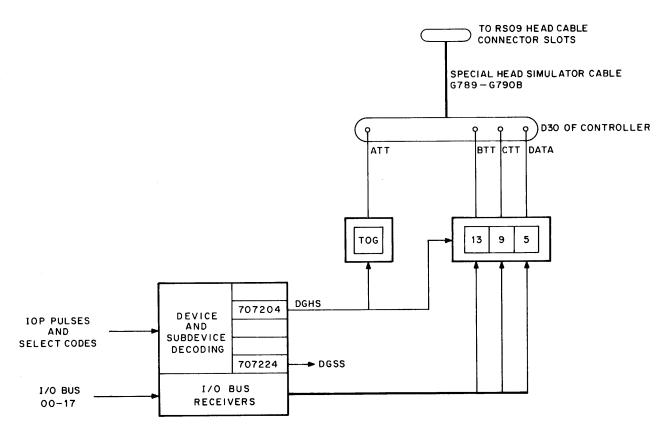

| 1.3       The Operator's Controls       1-16         1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2         DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.2       G26 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board                                                                                                                                                          | 1.2.2.3   | Maintenance Section                   |      |

| 1.3.1       Transfer Rate Selection       1-16         1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9 </td <td>1.3</td> <td>The Operator's Controls</td> <td></td>                                                                                | 1.3       | The Operator's Controls               |      |

| 1.3.2       Disk Address Selection Jacks       1-19         1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10 <td< td=""><td>1.3.1</td><td></td><td></td></td<>                                                                                               | 1.3.1     |                                       |      |

| 1.3.3       Write Lockout Switches       1-19         1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.1.3       Loading       2-2         2.2       G985 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator                                                                                                                                           | 1.3.2     | Disk Address Selection Jacks          |      |

| 1.4       The Operator's Indicators       1-21         1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                       | 1.3.3     |                                       |      |

| 1.5       Programming Examples       1-22         1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                              |           |                                       |      |

| 1.6       Programming With the ADS Register       1-25         1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                |           |                                       |      |

| 1.7       Programming Multiple Disk Systems       1-27         1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |      |

| 1.8       Using DECdisk in a System       1-27         1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                       |      |

| 1.9       Summary of DECdisk Characteristics       1-29         CHAPTER 2 DECDISK MODULES         2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | · · · · · · · · · · · · · · · · · · · |      |

| CHAPTER 2 DECDISK MODULES           2.1         Introduction         2-1           2.1.1         Types of Modules         2-1           2.1.2         Measurement Definitions         2-2           2.1.3         Loading         2-2           2.2         G085 Disk Read Amplifier         2-3           2.3         G285 Series Switch         2-7           2.4         G286 Centertap Selector         2-10           2.5         G290 Writer Flip-Flop         2-13           2.6         G681 B Track Matrix         2-16           2.7         G711 RF08 Terminator Board         2-16           2.8         G775 Indicator Panel         2-16           2.9         G789 Signal Simulator Connector         2-16           2.10         G790 Signal Simulator Generator         2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                       |      |

| 2.1       Introduction       2-1         2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •••       |                                       | 1-27 |

| 2.1.1       Types of Modules       2-1         2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHAPTER 2 | DECDISK MODULES                       |      |

| 2.1.2       Measurement Definitions       2-2         2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.1       | Introduction                          | 2-1  |

| 2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.1.1     | Types of Modules                      | 2-1  |

| 2.1.3       Loading       2-2         2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.1.2     | Measurement Definitions               | 2-2  |

| 2.2       G085 Disk Read Amplifier       2-3         2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.3     |                                       |      |

| 2.3       G285 Series Switch       2-7         2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2       |                                       |      |

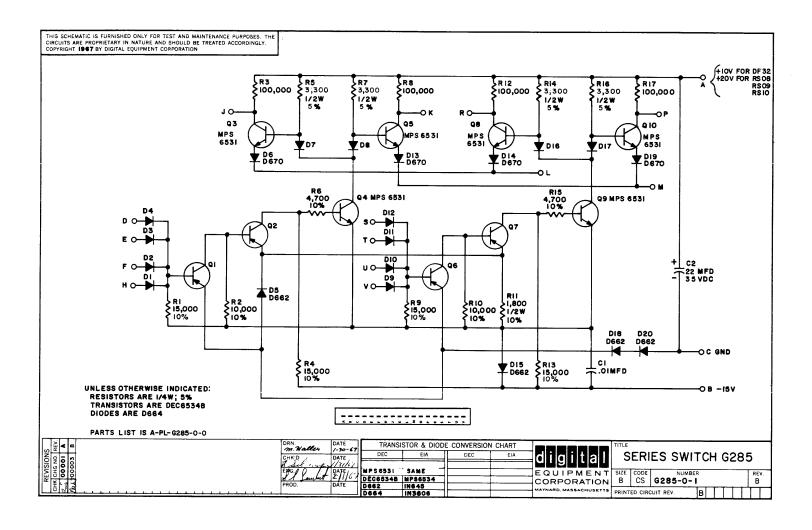

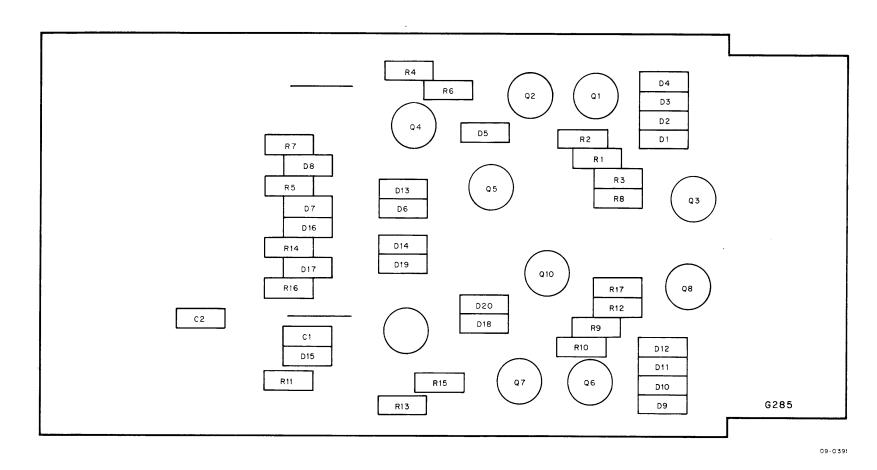

| 2.4       G286 Centertap Selector       2-10         2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3       |                                       |      |

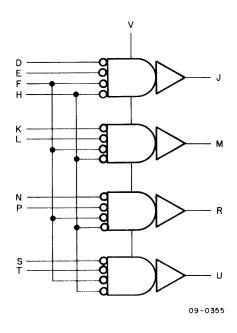

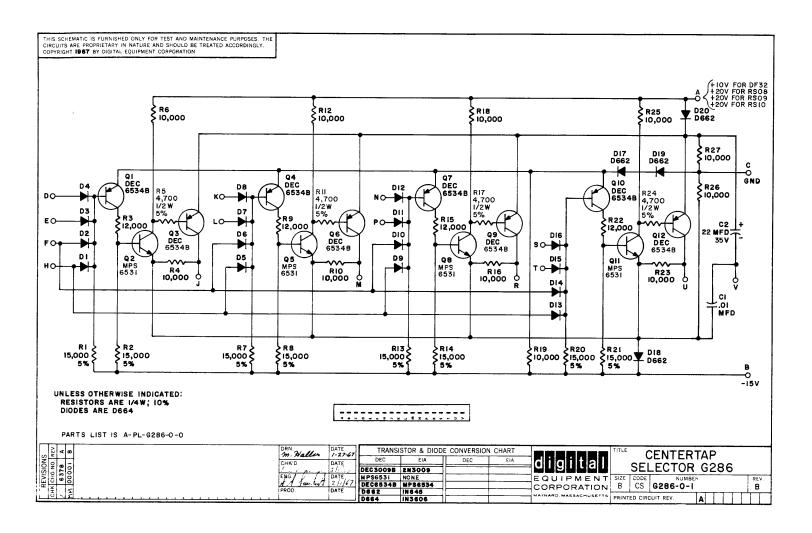

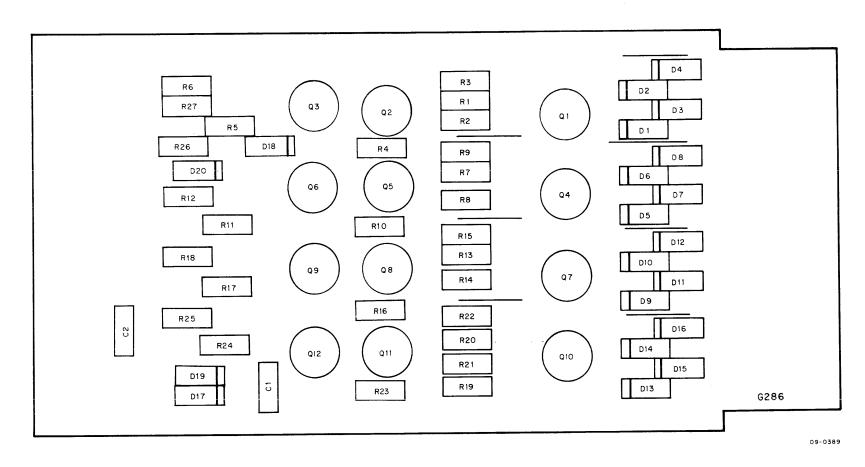

| 2.5       G290 Writer Flip-Flop       2-13         2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.4       | G286 Centertap Selector               |      |

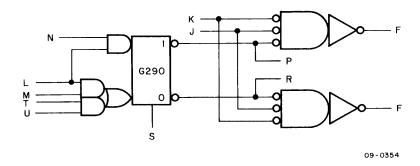

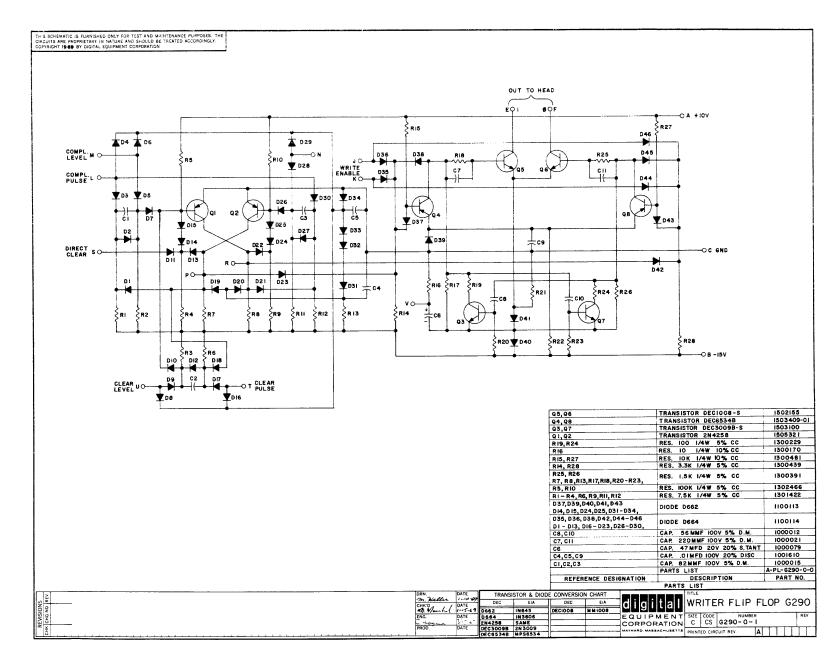

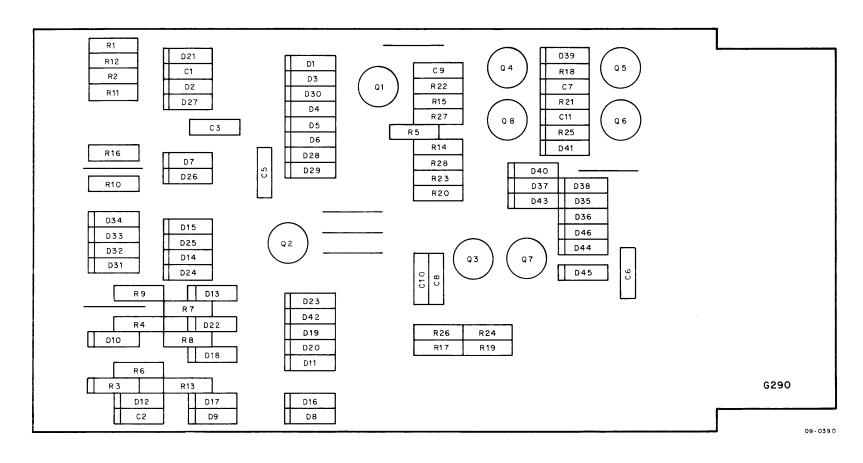

| 2.6       G681 B Track Matrix       2-16         2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.5       |                                       |      |

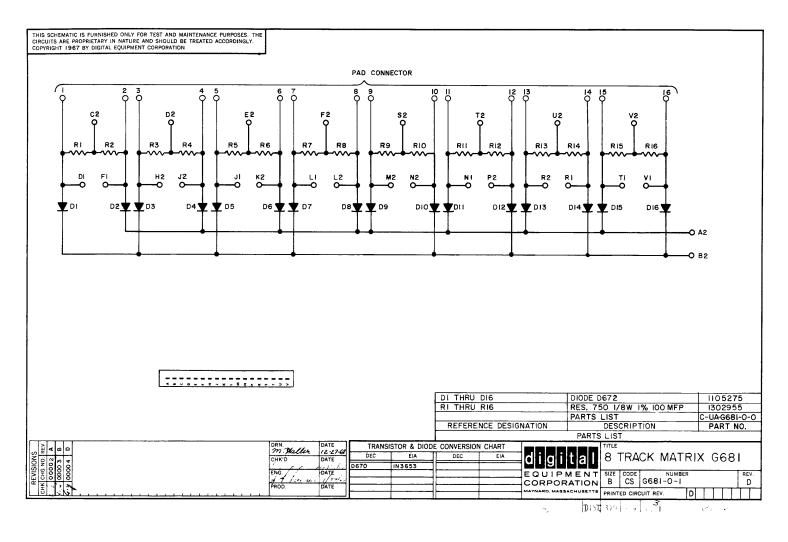

| 2.7       G711 RF08 Terminator Board       2-16         2.8       G775 Indicator Panel       2-16         2.9       G789 Signal Simulator Connector       2-16         2.10       G790 Signal Simulator Generator       2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.6       |                                       |      |

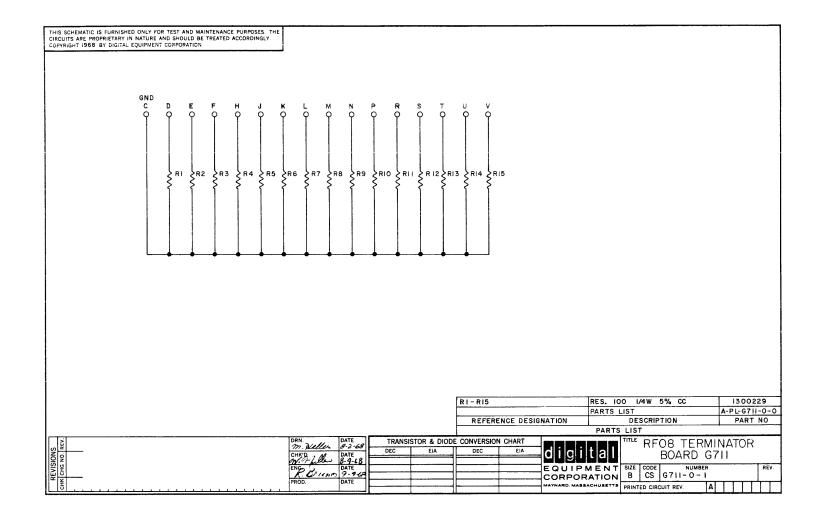

| 2.8G775 Indicator Panel2-162.9G789 Signal Simulator Connector2-162.10G790 Signal Simulator Generator2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                       |      |

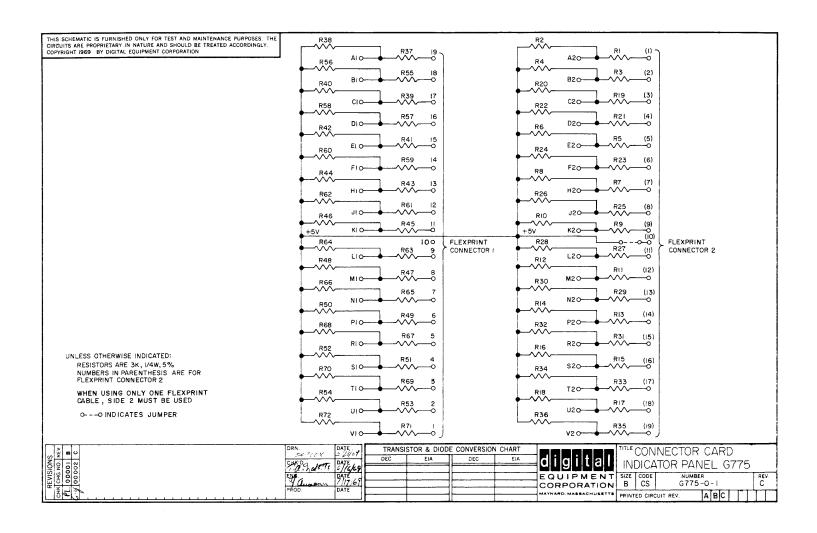

| 2.9 G789 Signal Simulator Connector 2-16 2.10 G790 Signal Simulator Generator 2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                       |      |

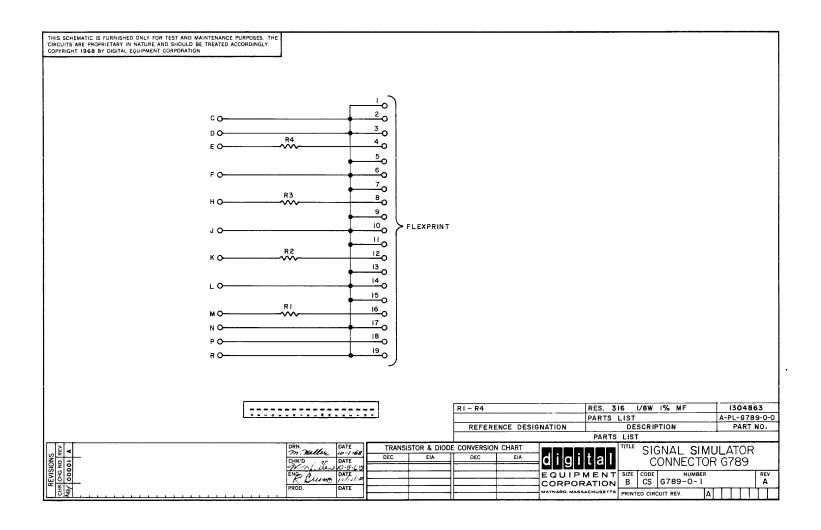

| 2.10 G790 Signal Simulator Generator 2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                       |      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | _                                     |      |

## **CONTENTS (Cont)**

|         |                                                          | Page |  |  |

|---------|----------------------------------------------------------|------|--|--|

| 2.12    | M104 Multiplexer Module                                  | 2-24 |  |  |

| 2.13    | M216 Six Flip-Flops                                      | 2-29 |  |  |

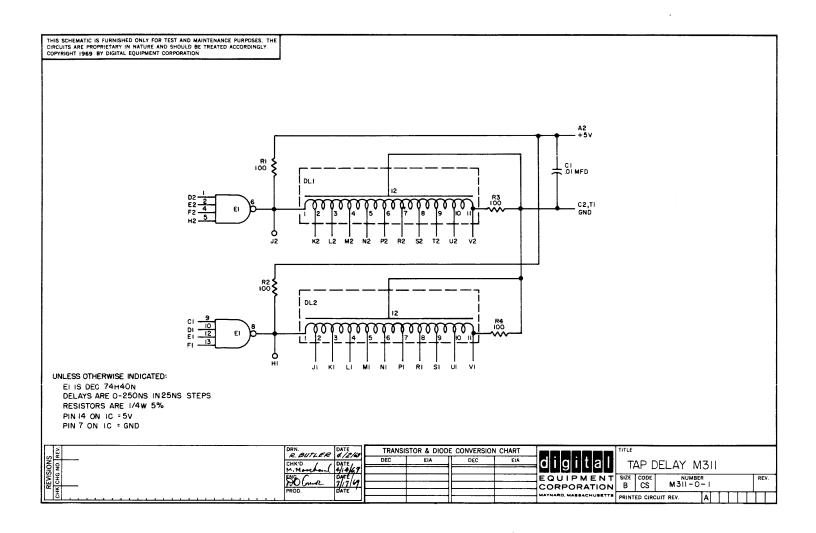

| 2.14    | M311 Tapped Delay Line                                   | 2-31 |  |  |

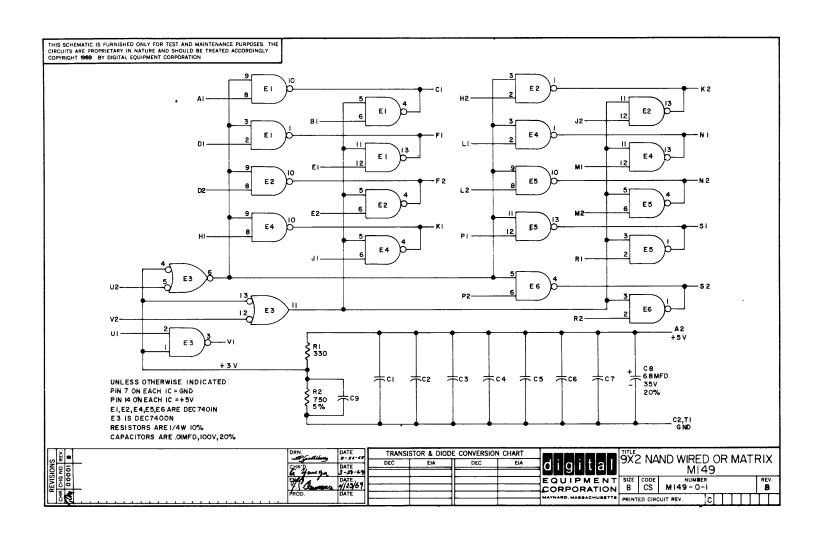

| 2.15    | M149 9 X 2 NAND "Wired OR" Matrix                        | 2-33 |  |  |

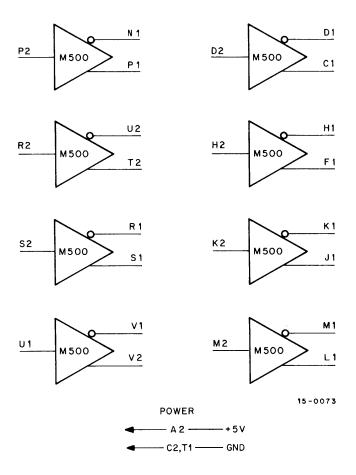

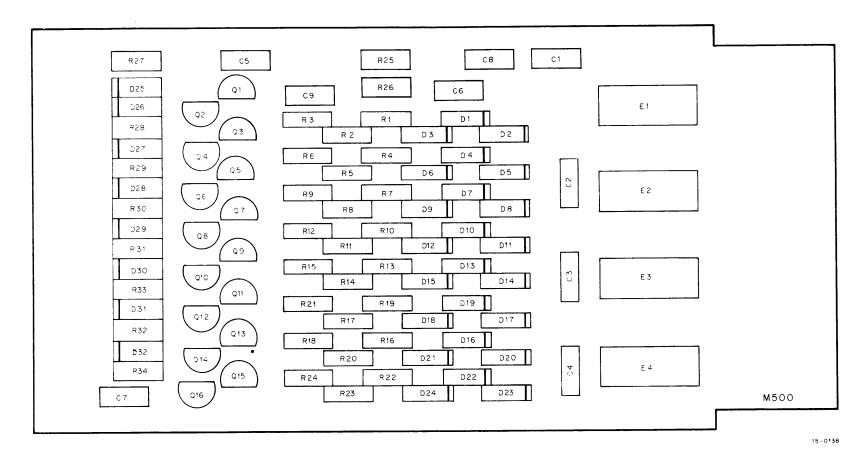

| 2.16    | M500 Negative Receiver Module                            | 2-33 |  |  |

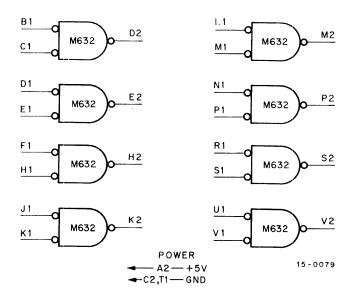

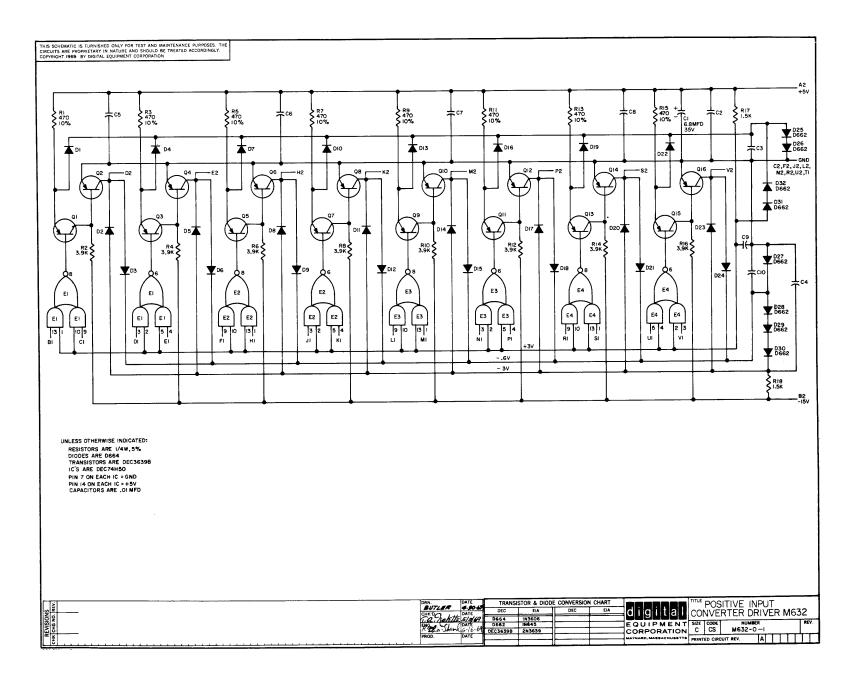

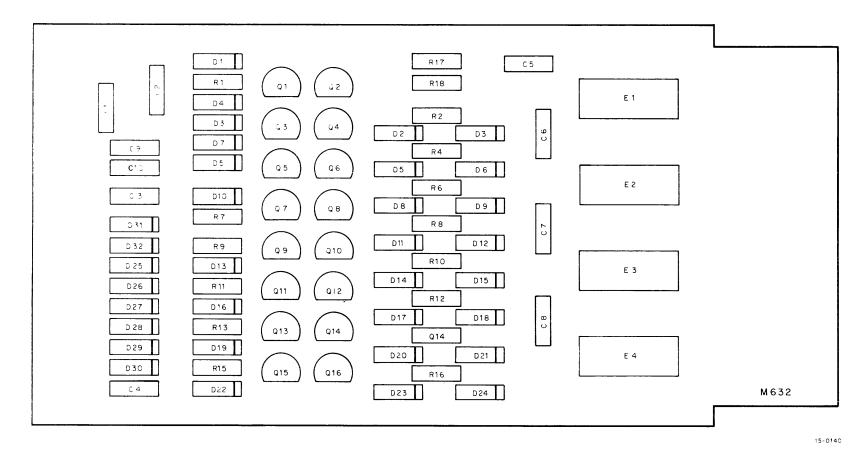

| 2.17    | M632 Negative Driver Module                              | 2-38 |  |  |

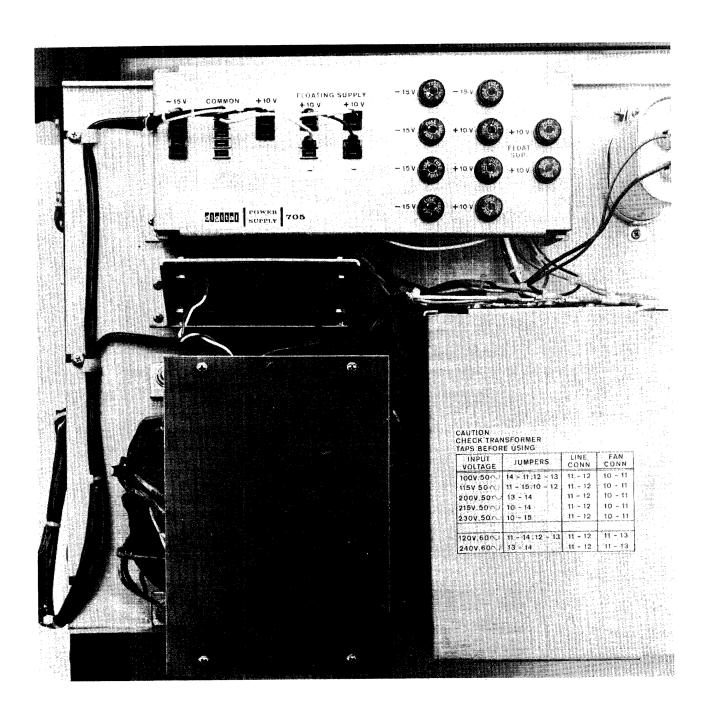

| 2.18    | 705B Power Supply                                        | 2-41 |  |  |

| 2.19    | 716 Indicator Supply                                     | 2-41 |  |  |

| 2.20    | 855 Power Control                                        | 2-45 |  |  |

| CHAPTER | 3 RS09 DISK DRIVE                                        |      |  |  |

| 3.1     | Read/Write Heads                                         | 3-1  |  |  |

| 3.2     | Digital Recording Techniques                             | 3-4  |  |  |

| 3.3     | The Read/Write Head Electronics                          | 3-5  |  |  |

| 3.4     | The DECdisk Signal Format                                | 3-7  |  |  |

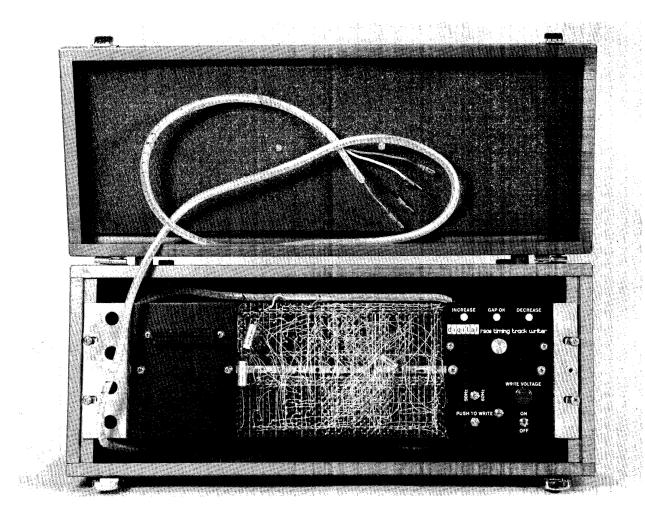

| 3.5     | The Timing Track Writer                                  | 3-12 |  |  |

| CHAPTER | 4 DECDISK LOGIC                                          |      |  |  |

| 4.1     | Signal Error Detecting Circuits                          | 4-1  |  |  |

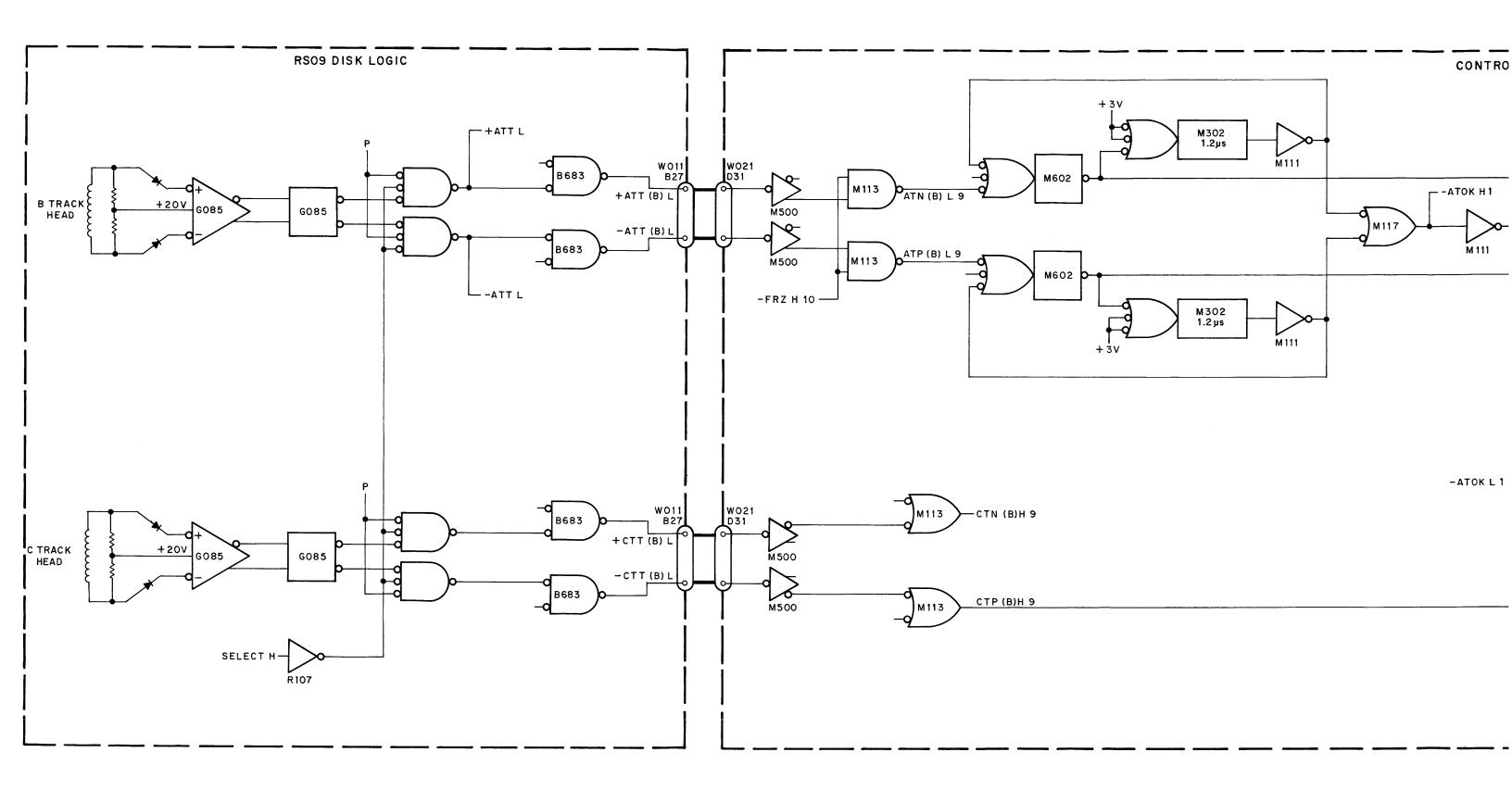

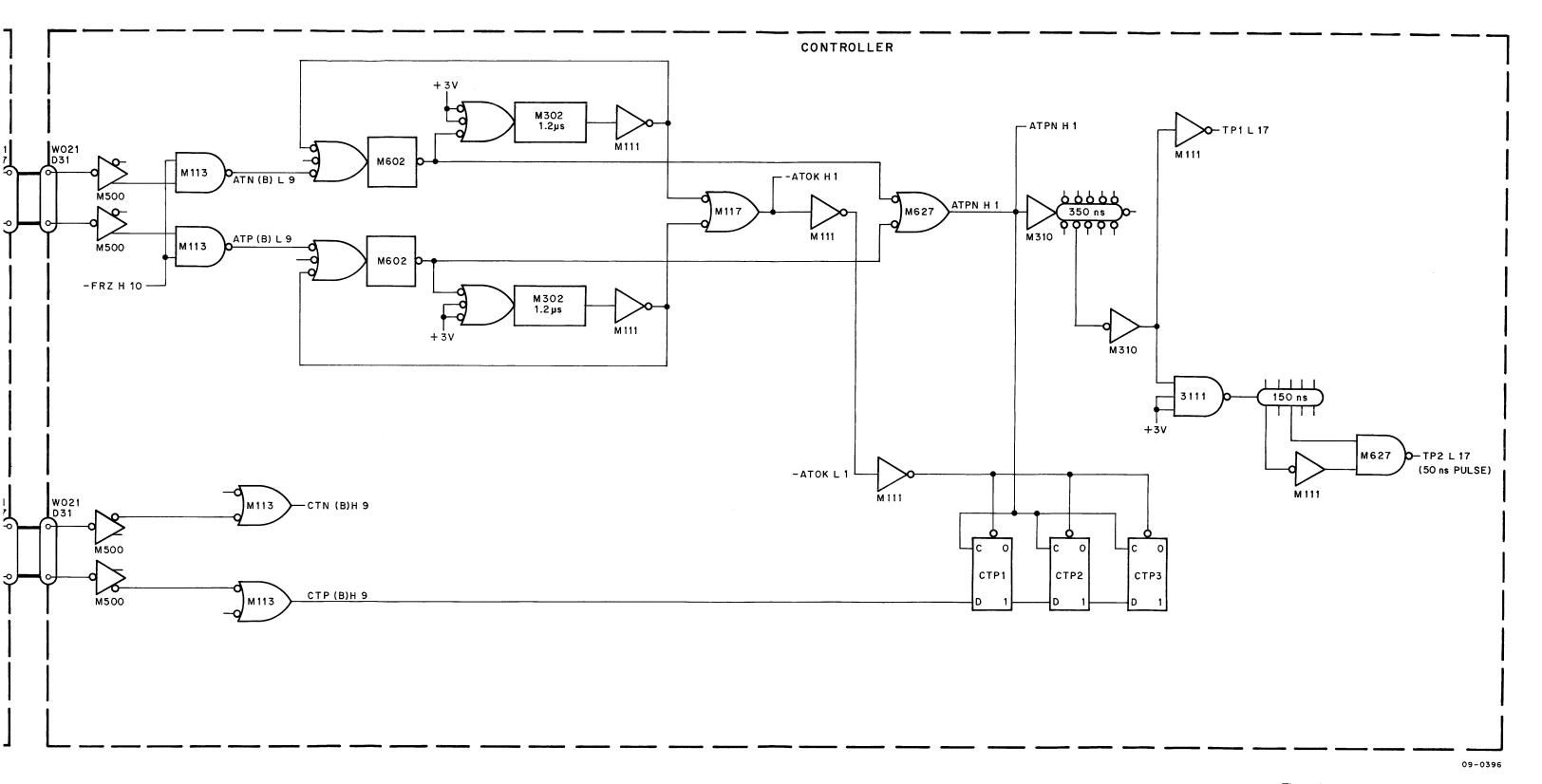

| 4.1.1   | Error Detection Logic for the A Timing Track             | 4-1  |  |  |

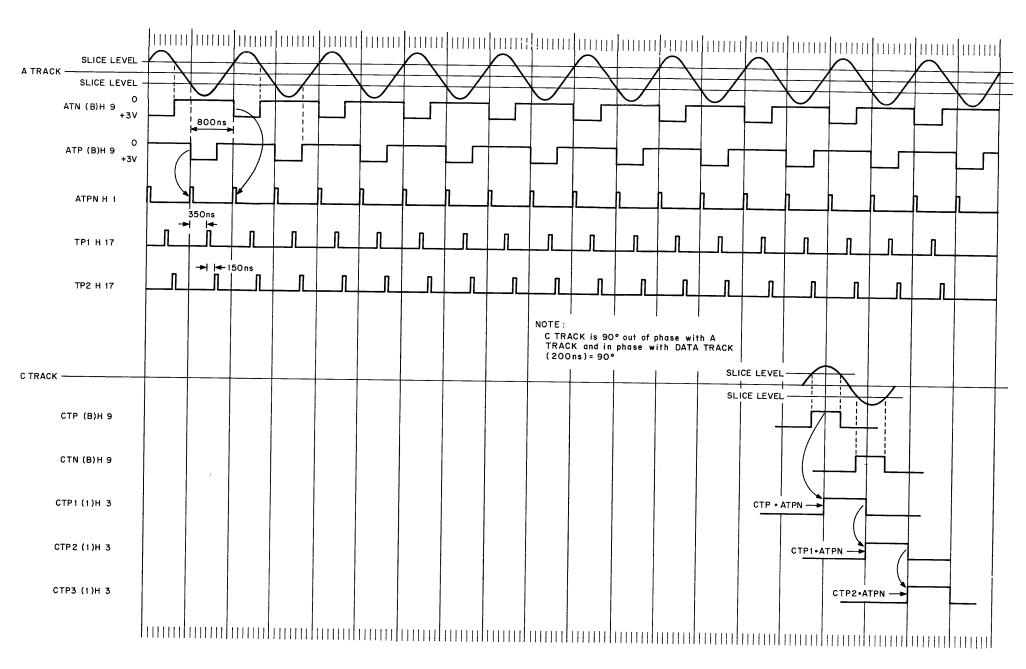

| 4.1.2   | Error Detection Logic for the B and C Tracks             |      |  |  |

| 4.1.3   | Error Detection Logic for the Data Tracks                |      |  |  |

| 4.2     | The Control Section Logic                                | 4-7  |  |  |

| 4.2.1   | The IOT Decode and Trap Logic                            | 4-7  |  |  |

| 4.2.2   | The Function Register                                    | 4-10 |  |  |

| 4.2.3   | The Timing Generator                                     | 4-10 |  |  |

| 4.2.4   | The Unlock Sequence Logic                                | 4-10 |  |  |

| 4.2.5   | The Track and Disk Address Register                      | 4-10 |  |  |

| 4.2.6   | The Word Address Register                                | 4-17 |  |  |

| 4.2.7   | The Disk Segment Register and Transfer Rate Select Logic | 4-17 |  |  |

| 4.2.8   | Equal Comparison Gating                                  | 4-23 |  |  |

| 4.2.9   | The Address of the Disk Segment Register (ADS)           | 4-24 |  |  |

| 4.3     | The Data Section Logic                                   | 4-25 |  |  |

| 4.3.1   | The Buffer and Shift Registers                           | 4-25 |  |  |

| 4.3.2   | The WRITE Operation and its Associated Logic             | 4-25 |  |  |

| 4.3.3   | The READ Operation and its Associated Logic              | 4-25 |  |  |

| 4.3.4   | The WRITE CHECK Operation and its Associated Logic       | 4-37 |  |  |

| 4.3.5   | Error Flags                                              | 4-37 |  |  |

| 4.3.5.1 | WRITE CHECK Error                                        | 4-37 |  |  |

| 4.3.5.2 | Error and FReeZe                                         | 4-41 |  |  |

| 4.3.5.3 | Address Parity Error                                     |      |  |  |

## CONTENTS (Cont)

|           |                                                | Page       |  |

|-----------|------------------------------------------------|------------|--|

| 4.3.5.4   | Missed Transfer Error                          | 4-41       |  |

| 4.3.5.5   | Data Parity Error                              | 4-42       |  |

| 4.3.5.6   | NonExistent Disk Error (PSLER)                 | 4-44       |  |

| 4.3.5.7   | Write LockOut Error                            | 4-44       |  |

| 4.3.5.8   | NonExistent Disk (SEQ ER)                      | 4-44       |  |

| 4.3.5.9   | Data Channel Timing Error                      | 4-46       |  |

| 4.3.5.10  | Program Error                                  | 4-46       |  |

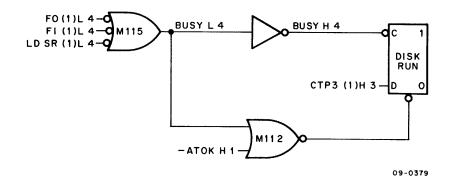

| 4.3.6     | Automatic Priority and Program Interrupt Logic | 4-46       |  |

| 4.3.7     | The A TEST and Read Disable Signal             | 4-48       |  |

| 4.3.8     | The Gap                                        | 4-49       |  |

| 4.3.9     | The Maintenance Logic                          | 4-49       |  |

| CHAPTER 5 | FIELD INSTALLATION                             |            |  |

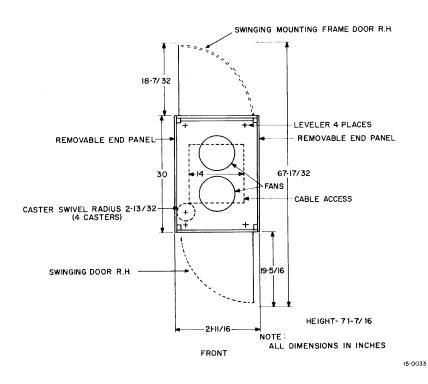

| 5.1       | Installation Location                          | 5-1        |  |

| 5.2       | Environmental Considerations                   | 5-1        |  |

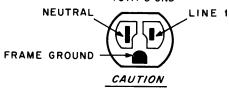

| 5.3       | Primary Power Requirements                     | 5-1        |  |

| 5.4       | Accessories                                    | 5-4        |  |

| 5.5       | npacking, and Installation                     |            |  |

| 5.5.1     | Cabinet Unpacking                              |            |  |

| 5.5.2     | Cabinet Installation                           | 5-4        |  |

| 5.5.3     | RF09 Controller Installation                   | 5-6        |  |

| 5.5.4     | RS09 Unpacking                                 | 5-6        |  |

| 5.5.5     | RS09 Installation                              | 5-6        |  |

| 5.6       | Power-Up Sequence                              |            |  |

| 5.7       | Acceptance Procedure                           | 5-11       |  |

| 5.7.1     | Acceptance Forms                               | 5-11       |  |

| 5.7.2     | Diagnostics                                    | 5-11       |  |

| 5.7.3     | System Software                                | 5-11       |  |

| 5.8       | Shipping                                       | 5-11       |  |

| CHAPTER 6 | ORGANIZATIONAL MAINTENANCE                     |            |  |

| 6.1       | Preventive Maintenance                         | 6-1        |  |

| 6.2       | RS09 Adjustments                               | 6-3        |  |

| 6.2.1     | Measuring the Gain                             |            |  |

| 6.2.2     | Measuring the Slice                            | 6-3<br>6-4 |  |

| 6.2.3     | Calibrating the Read Amplifiers                | 6-4        |  |

| 6.2.4     | Changing the Timing Tracks                     |            |  |

| 6.3       | Diagnostics 6                                  |            |  |

|           |                                                |            |  |

## **CONTENTS** (Cont)

|           |                                          | Page |

|-----------|------------------------------------------|------|

| CHAPTER 7 | FIELD LEVEL MAINTENANCE                  |      |

| 7.1       | Field Level RS09 and RF09 Maintenance    | 7-1  |

| 7.1.1     | RF09 Off-Line Checkout Without the RS09  | 7-1  |

| 7.1.2     | RF09 Off-Line Checkout With the RS09     | 7-2  |

| 7.2       | Field Level Disk Assembly Repairs        | 7-2  |

| 7.2.1     | Removing the Disk Assembly               | 7-3  |

| 7.2.2     | Removing the Disk Surface                | 7-3  |

| 7.2.3     | Replacing the Shoes                      | 7-9  |

| 7.2.4     | Replacing the Disk Surface               | 7-10 |

| 7.2.5     | Rewriting the Timing Tracks              | 7-10 |

| 7.3       | Field Level RS09 Calibration             | 7-14 |

| 7.3.1     | Measuring Surface Modulation             | 7-14 |

| 7.3.2     | Analyzing the Gain of the Data Tracks    | 7-16 |

| 7.3.3     | Calibrating the Gain of the Data Readers | 7-19 |

## APPENDIX A RF09 SIGNAL SUMMARY

### APPENDIX B RS09 SIGNAL SUMMARY

## **ILLUSTRATIONS**

| Figure No. | Figure No. Title                                               |         | Page |

|------------|----------------------------------------------------------------|---------|------|

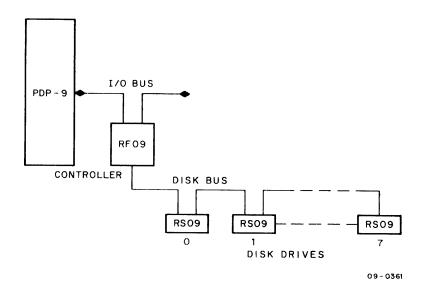

| 1-1        | DECdisk System Configurations                                  | 09-0361 | 1-2  |

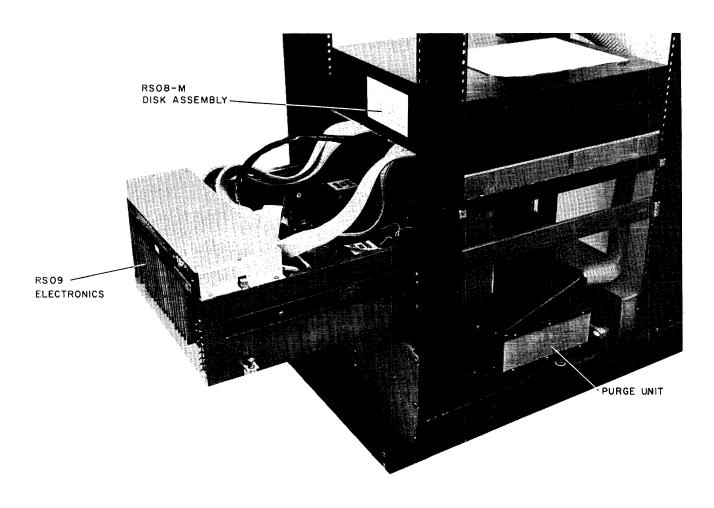

| 1-2        | RS09 Disk Drive                                                | 5003-5  | 1-2  |

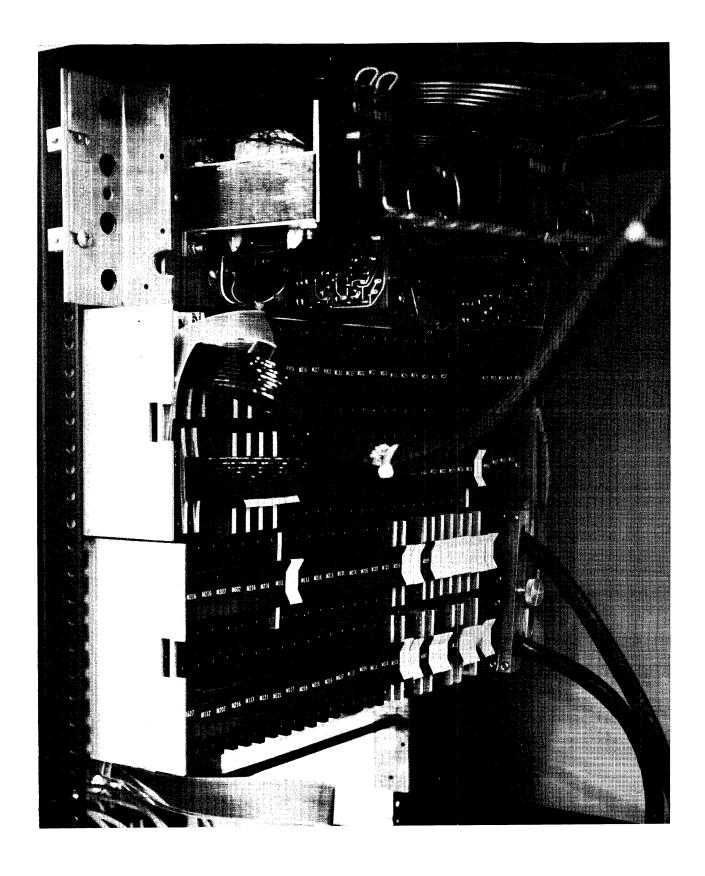

| 1-3        | RF09 Controller                                                | 5030-2  | 1-4  |

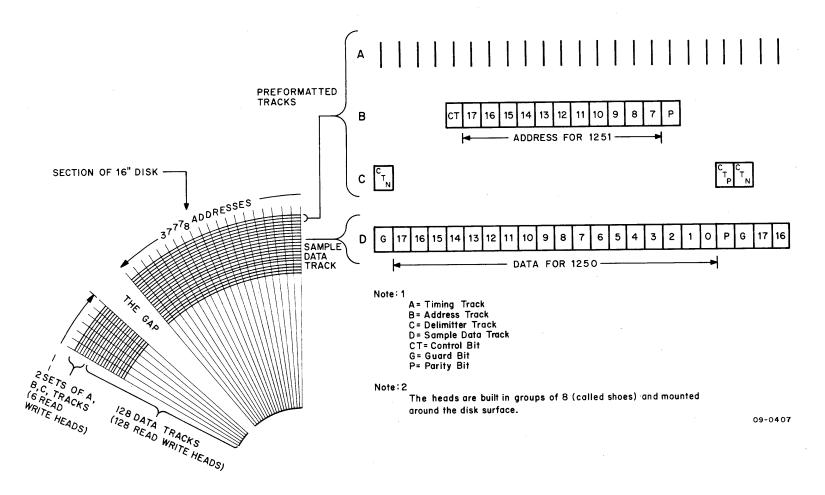

| 1-4        | Disk Surface Recording Format                                  | 09-0407 | 1-5  |

| 1-5        | DECdisk Control Section                                        | 09-0413 | 1-7  |

| 1-6        | DECdisk Data Transfer Section                                  | 09-0358 | 1-9  |

| 1-7        | Simulating the Disk Surface with the Maintenance Logic         | 09-0393 | 1-17 |

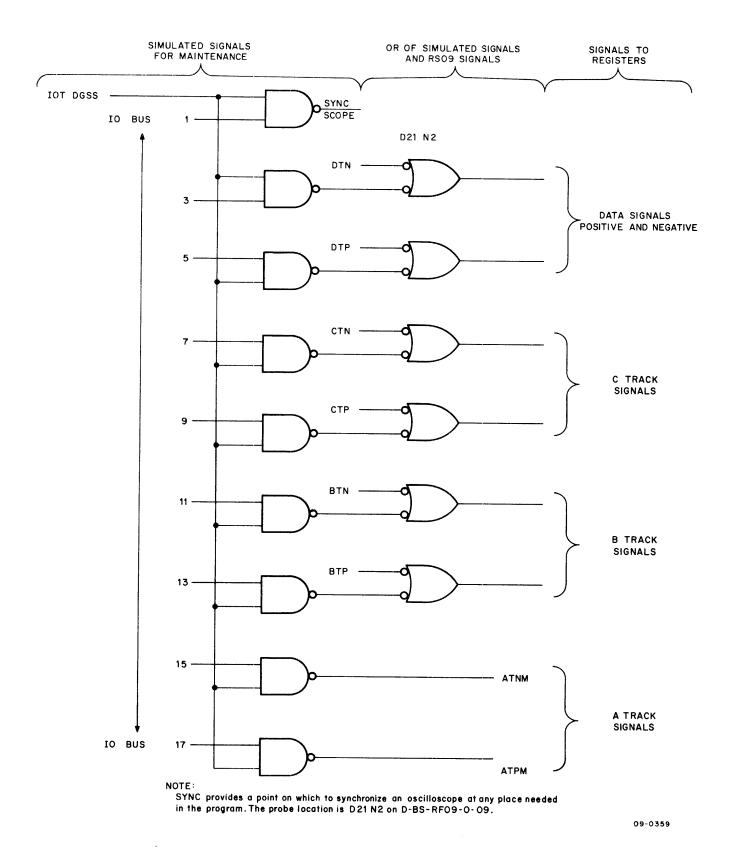

| 1-8        | Simulating the RS09 with the Maintenance Logic                 | 09-0359 | 1-18 |

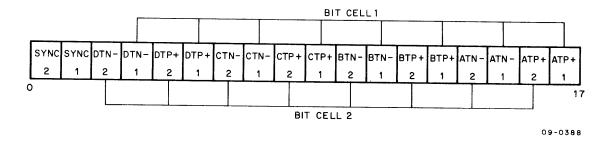

| 1-9        | AC Bit Usage for IOT DGSS                                      | 09-0388 | 1-19 |

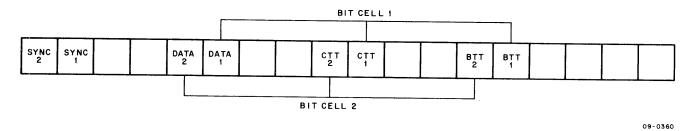

| 1-10       | AC Bit Usage for IOT DGHS                                      |         | 1-19 |

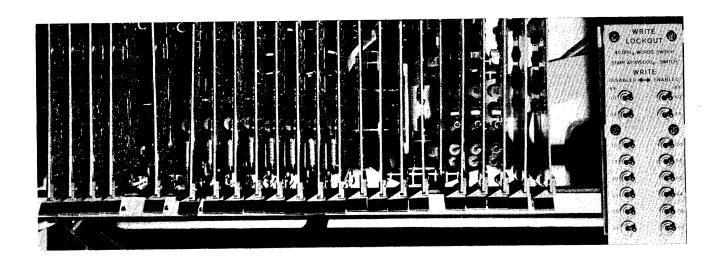

| 1-11       | Transfer Rate Selection Switch and Disk Address Select Jacks 5 |         | 1-20 |

| 1-12       | Write LockOut Switches                                         | 5003-1  | 1-20 |

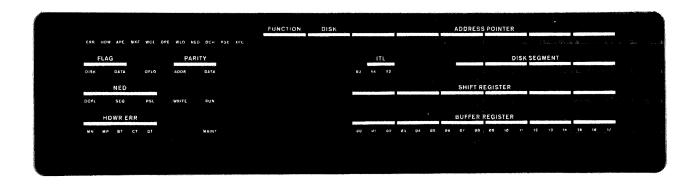

| 1-13       | Indicator Panel                                                | 5003-18 | 1-21 |

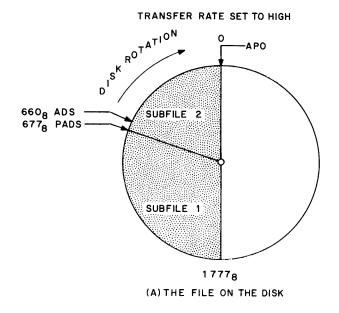

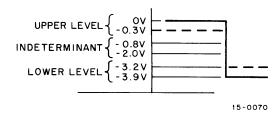

| 1-14       | Calculating Fast Access Calling                                | 09-0420 | 1-26 |

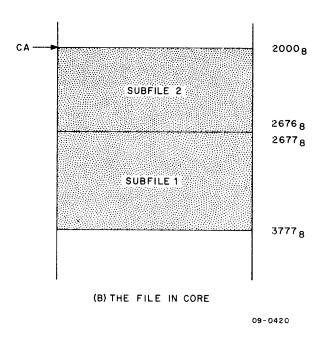

| 1-15       | Flow Diagram of the Subroutine That Uses the ADS Register      | 09-0421 | 1-28 |

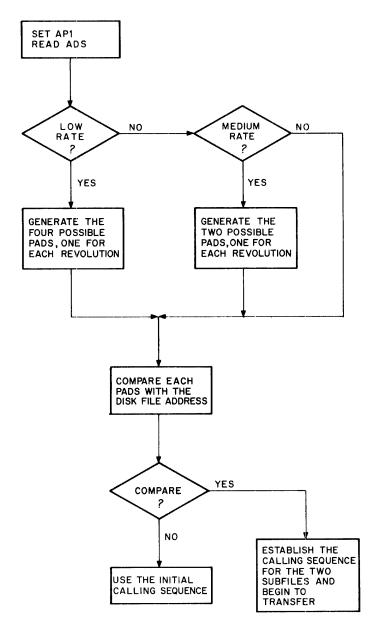

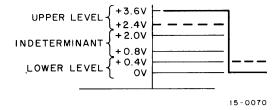

| 2-1        | Voltage Spectrum of Negative Logic System                      | 15-0070 | 2-1  |

| 2-2        | Voltage Spectrum of TTL Logic                                  | 15-0070 | 2-1  |

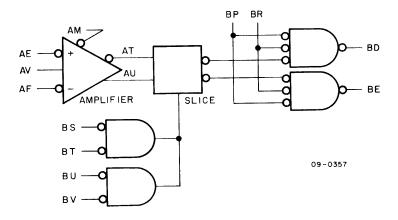

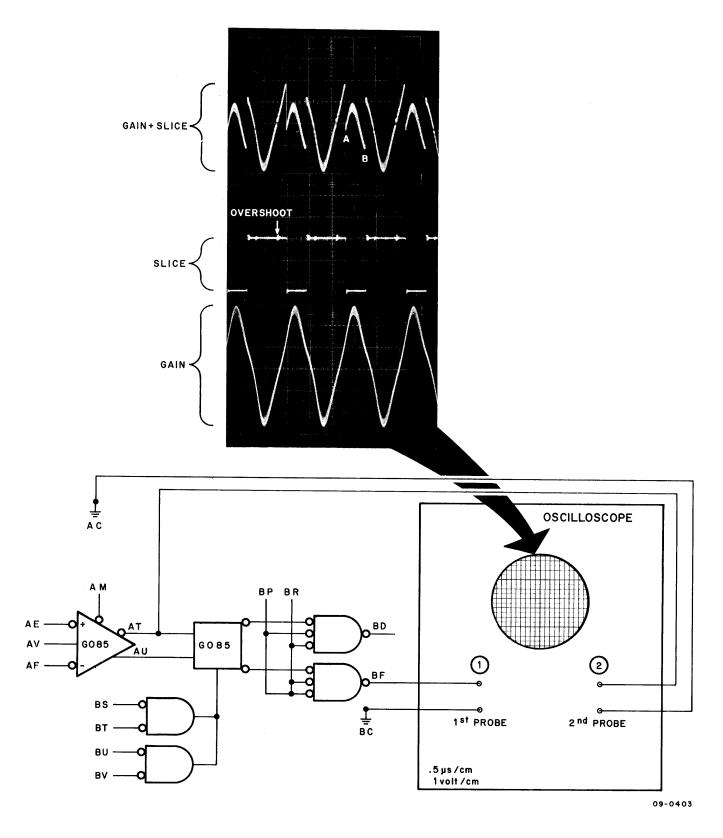

| 2-3        | G085 Disk Read Amplifier and Slice, Block Schematic 09-0357    |         | 2-3  |

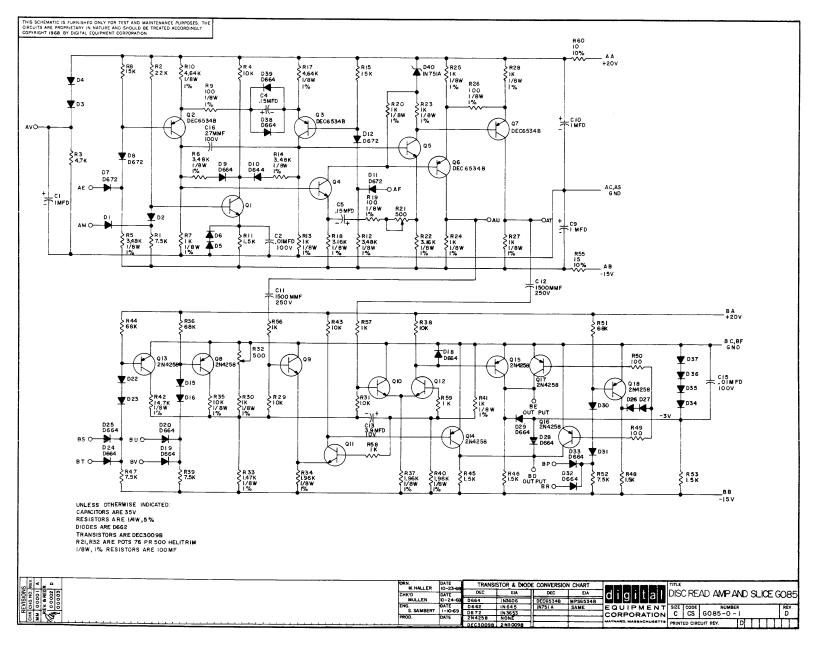

| 2-4        | G085 Disk Read Amplifier and Slice, Circuit Schematic C-C      |         | 2-4  |

## ILLUSTRATIONS (Cont)

| Figure No. | Title                                                   | Art No.       | Page |

|------------|---------------------------------------------------------|---------------|------|

| 2-5        | Disk Read Amplifier and Slice, Parts Location Diagram   | 09-0392       | 2-5  |

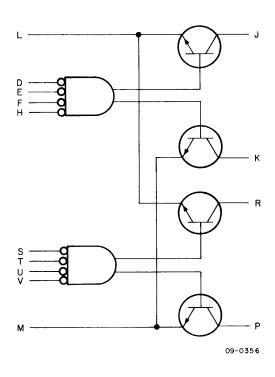

| 2-6        | G285 Series Switch, Block Schematic                     | 09-0356       | 2-7  |

| 2-7        | G285 Series Switch, Circuit Schematic                   | C-CS-G285-0-1 | 2-8  |

| 2-8        | G285 Series Switch, Parts Location Diagram              | 09-0391       | 2-9  |

| 2-9        | Centertap Selector, Block Schematic                     | 09-0355       | 2-10 |

| 2-10       | G286 Centertap Selector, Circuit Schematic              | C-CS-G286-0-1 | 2-11 |

| 2-11       | G286 Centertap Selector, Parts Location Diagram         | 09-0389       | 2-12 |

| 2-12       | The G290 Writer Flip-Flop, Block Schematic              | 09-0354       | 2-13 |

| 2-13       | G290 Writer Flip-Flop, Circuit Schematic                | C-CS-G290-0-1 | 2-14 |

| 2-14       | G290 Writer Flip-Flop, Parts Location Diagram           | 09-0390       | 2-15 |

| 2-15       | G681 Track Matrix, Circuit Schematic                    | B-CS-G681-0-1 | 2-17 |

| 2-16       | G711 RF08 Terminator Board, Circuit Schematic           | B-CS-G711-0-1 | 2-18 |

| 2-17       | G775 Connector-Card Indicator Panel, Circuit Schematic  | B-CS-G775-0-1 | 2-19 |

| 2-18       | G789 Signal Simulator Connector, Circuit Schematic      | B-CS-G789-0-1 | 2-20 |

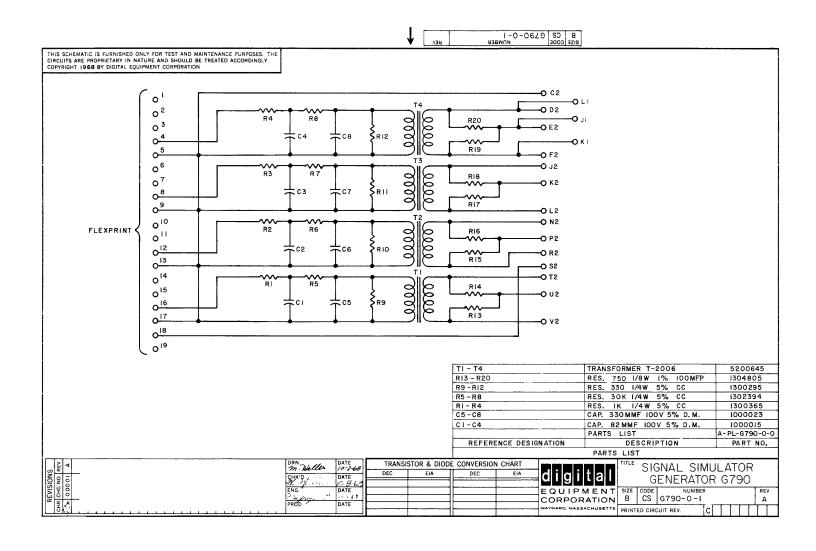

| 2-19       | G790 Signal Simulator Generator, Circuit Schematic      | B-CS-G790-0-1 | 2-22 |

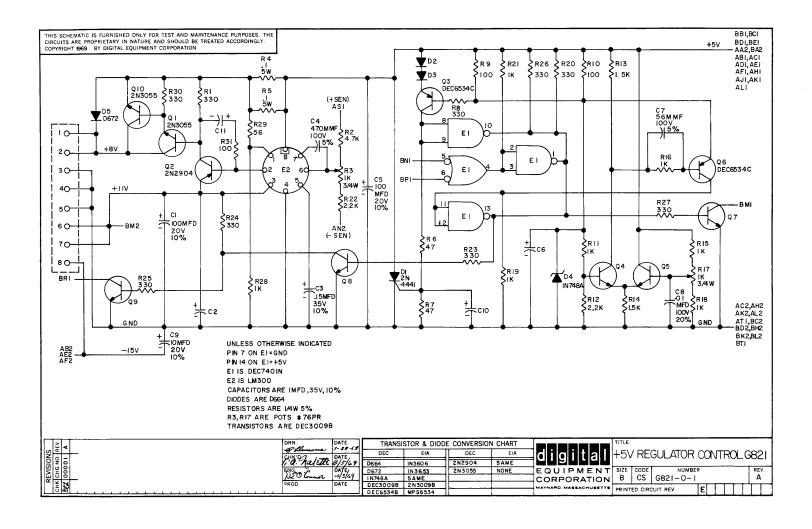

| 2-20       | G821 +5V Regulator Control, Circuit Schematic           | B-CS-G821-0-1 | 2-23 |

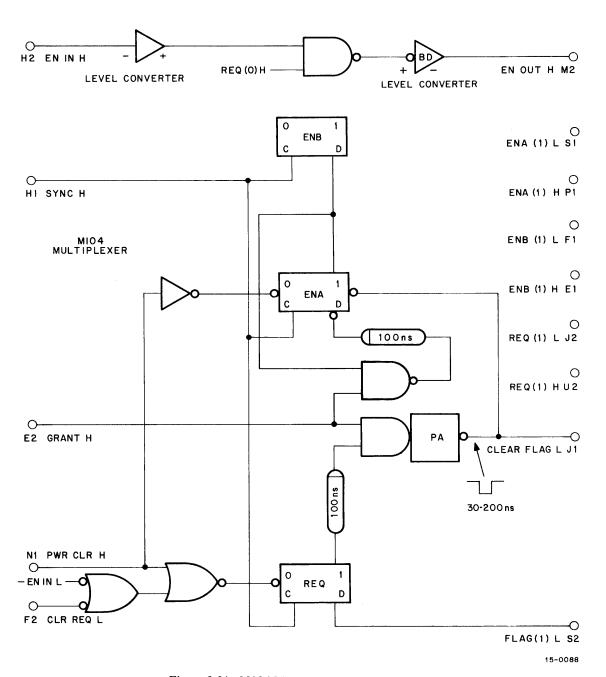

| 2-21       | M104 Multiplexer, Block Schematic                       |               | 2-25 |

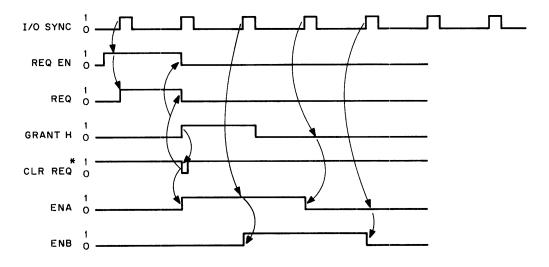

| 2-22       | M104, Multiplexer Timing Diagram                        | 15-0087       | 2-26 |

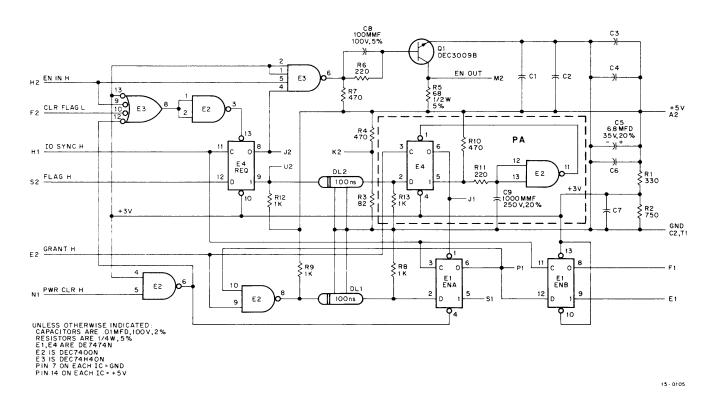

| 2-23       | M104 Multiplexer, Circuit Schematic                     | 15-0105       | 2-27 |

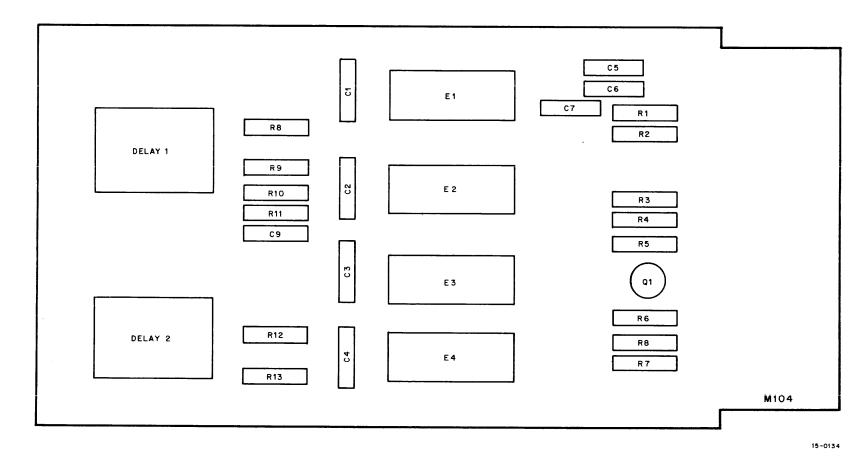

| 2-24       | M104 Multiplexer, Parts Location Diagram                | 15-0134       | 2-28 |

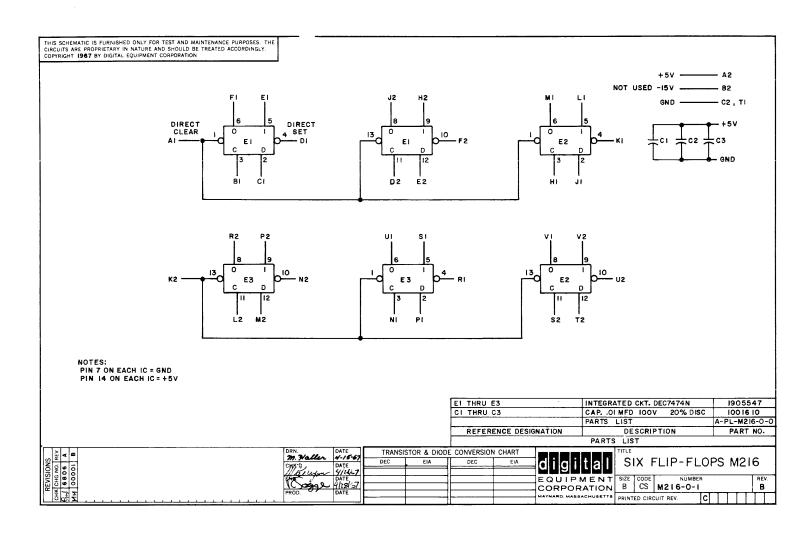

| 2-25       | M216 Six Flip-Flops, Circuit Schematic                  | B-CS-M216-0-1 | 2-30 |

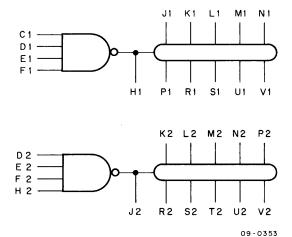

| 2-26       | M311 Tapped Delay, Block Schematic                      | 09-0353       | 2-31 |

| 2-27       | M311 Tapped Delay, Circuit Schematic                    | B-CS-M311-0-1 | 2-32 |

| 2-28       | M149 9 x 2 NAND Wired OR Matrix B-CS-M149-0-1           |               | 2-34 |

| 2-29       | M500 Negative Receiver, Block Schematic 15-0073         |               | 2-35 |

| 2-30       | M500 Negative Receiver, Circuit Schematic C-CS-M500-0-1 |               | 2-36 |

| 2-31       | M500 Negative Receiver, Parts Location Diagram          | 15-0138       | 2-37 |

| 2-32       | Negative Driver, Block Schematic                        | 15-0079       | 2-38 |

| 2-33       | M632 Negative Driver, Circuit Schematic                 | C-CS-M632-0-1 | 2-39 |

| 2-34       | M632 Negative Driver, Parts Location Diagram            | 15-0140       | 2-40 |

| 2-35       | 705B Power Supply                                       | 5003-17       | 2-42 |

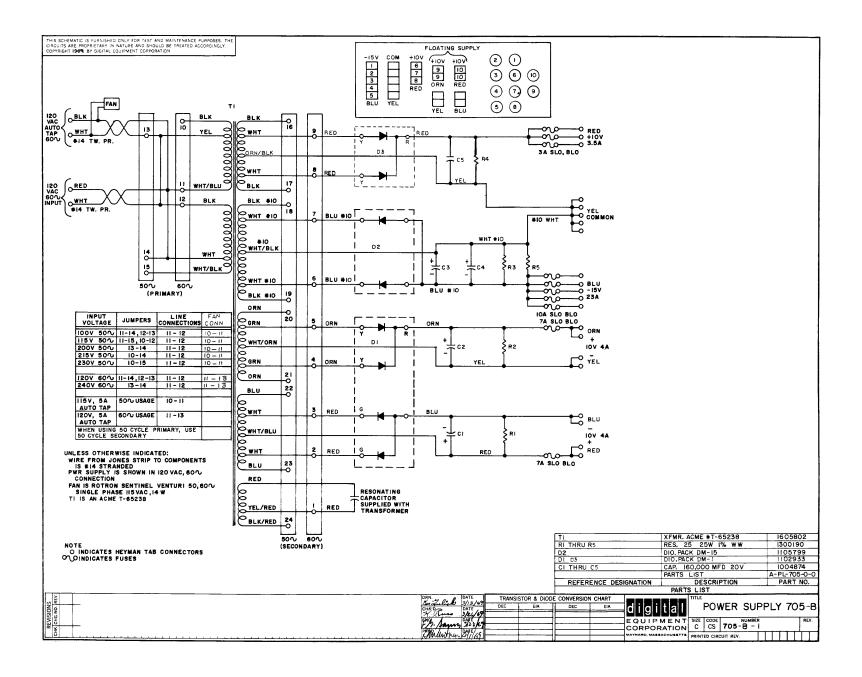

| 2-36       | 705B Power Supply, Circuit Schematic                    | C-CS-705B-1   | 2-43 |

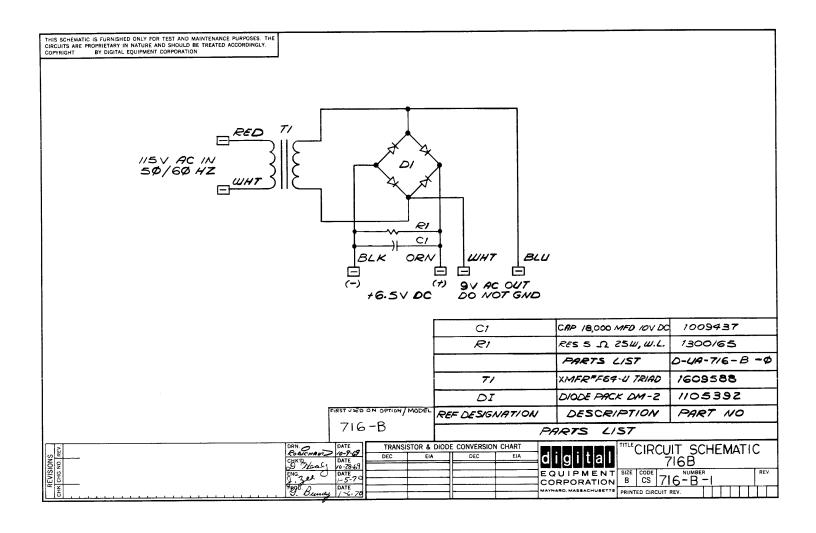

| 2-37       | 716 Indicator Supply, Circuit Schematic                 | B-CS-716-0-1  | 2-44 |

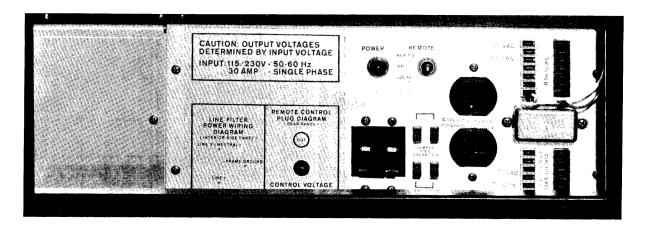

| 2-38       | 855 Power Control                                       | 5003-14       | 2-45 |

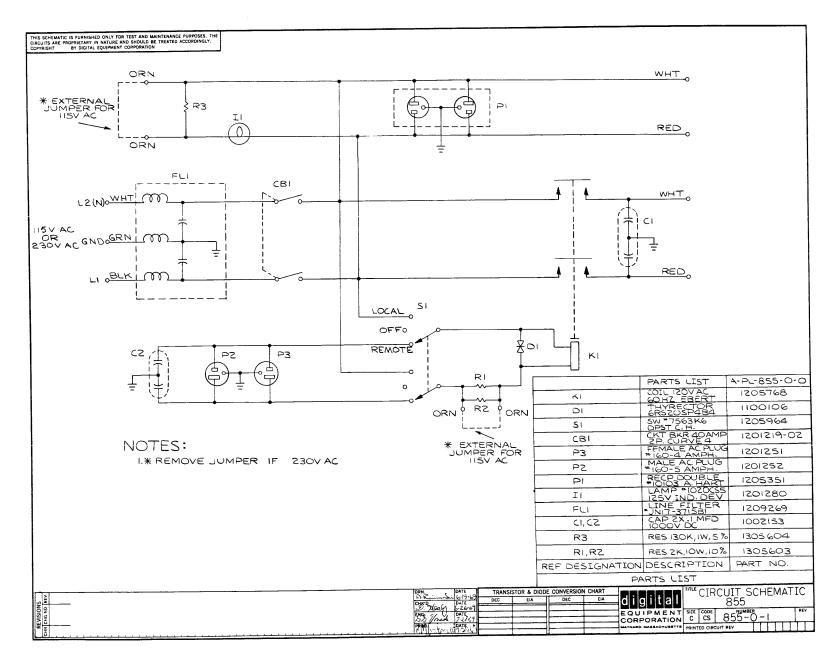

| 2-39       | 855 Power Control, Circuit Schematic                    | C-CS-855-0-1  | 2-46 |

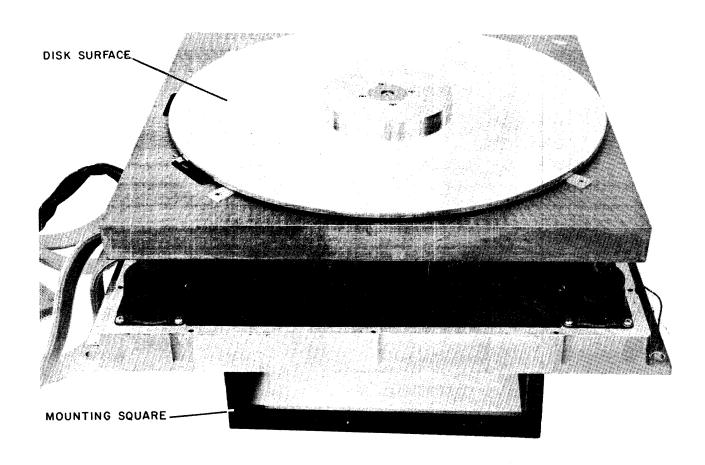

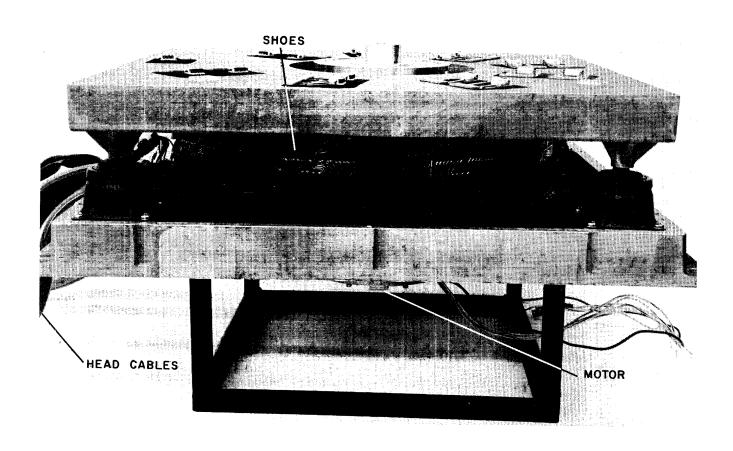

| 3-1        | Disk Assembly With Cover Removed                        | 5003-23       | 3-2  |

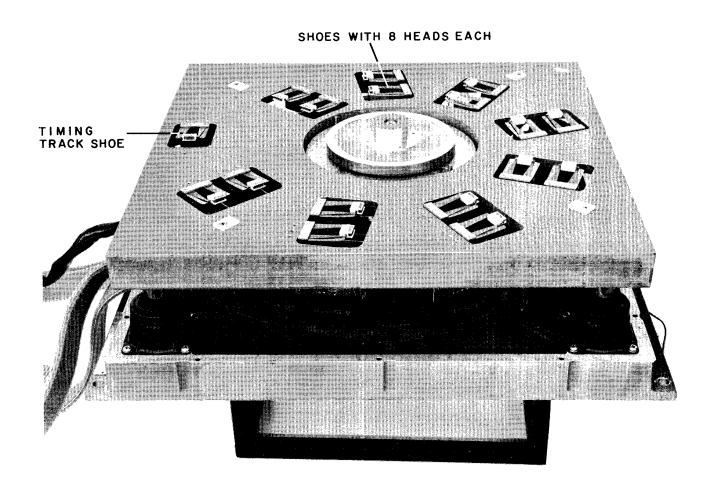

| 3-2        | Disk Assembly with Cover and Surface Removed            | 5003-26       | 3-3  |

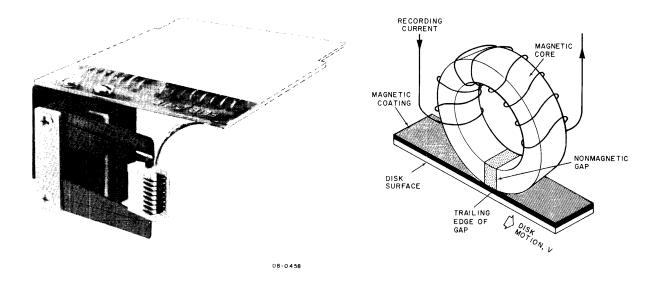

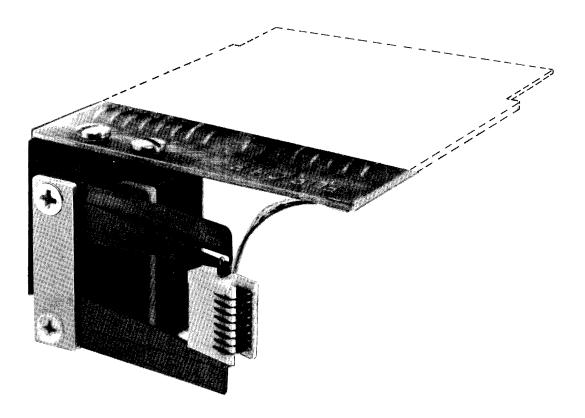

| 3-3        | (a) DECdisk Head Assembly and (b) Simplified Diagram    | 08-0458       | 3-4  |

|            | of the Magnetic Recording Process                       |               |      |

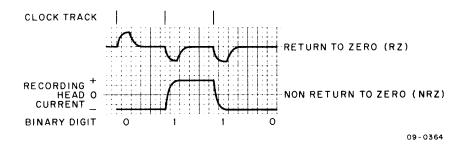

| 3-4        | NRZ and RZ Recording Formats                            | 09-0364       | 3-4  |

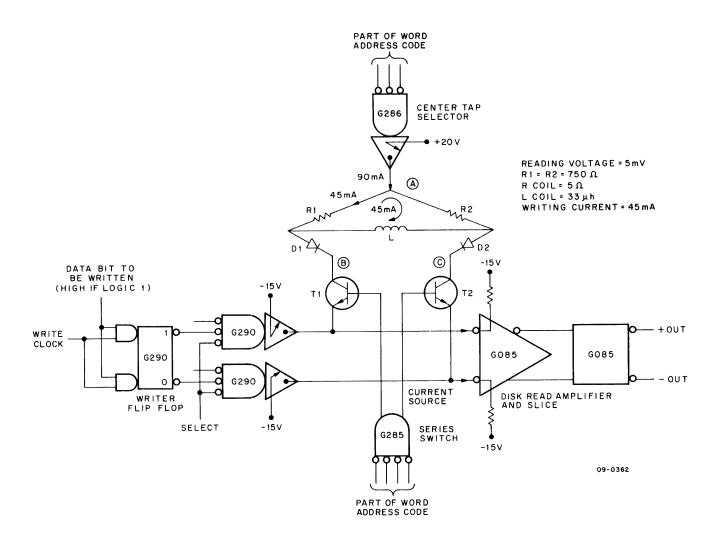

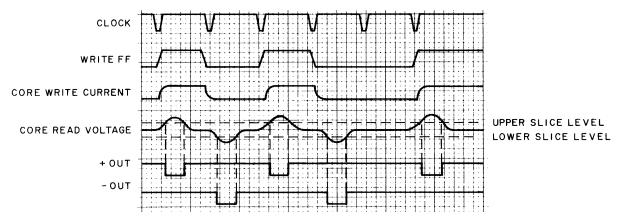

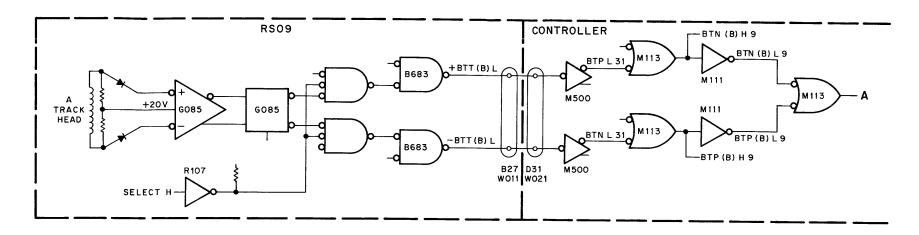

| 3-5        | DECdisk READ/WRITE Electronics                          | 09-0362       | 3-6  |

| 3-6        | READ/WRITE Electronics Waveforms 09-0363                |               | 3-7  |

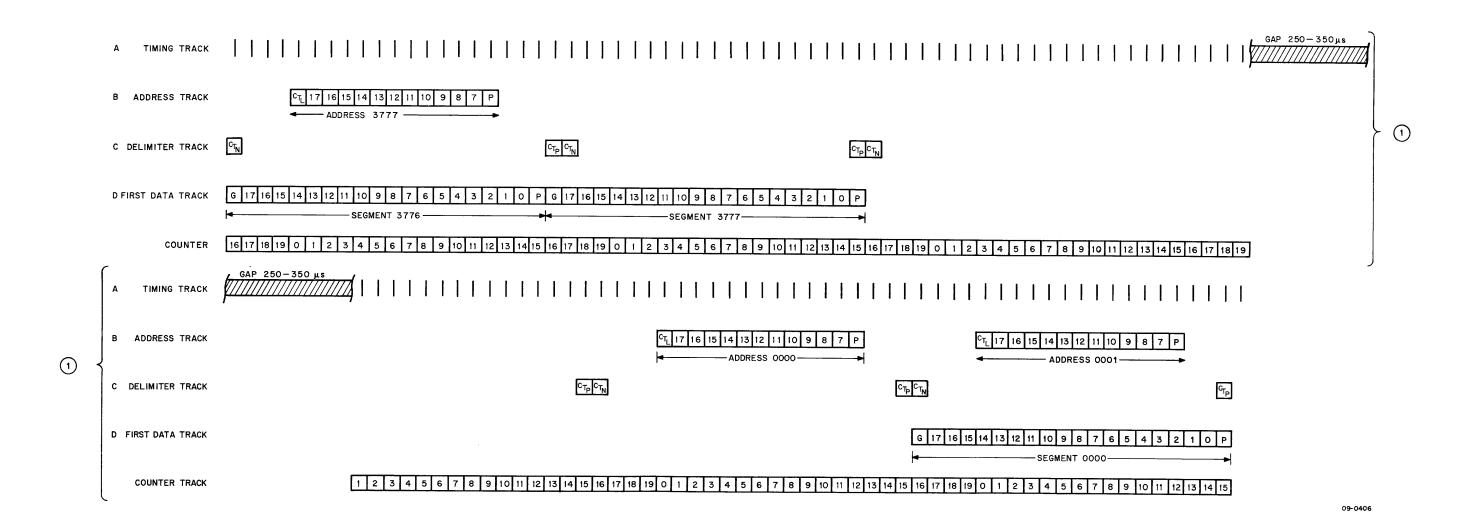

| 3-7        | DECdisk Format                                          | 09-0406       | 3-9  |

| 3-8        | Timing Track Writer                                     | 5099          | 3-11 |

## ILLUSTRATIONS (Cont)

| Figure No. | Title                                                    | Art No. | Page |

|------------|----------------------------------------------------------|---------|------|

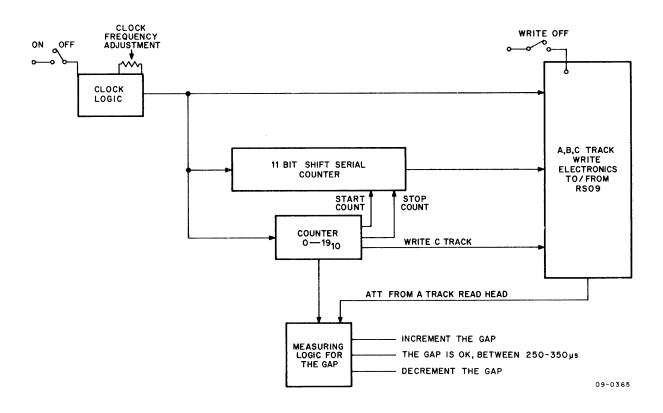

| 3-9        | Timing Track Writer, Block Diagram                       | 09-0365 | 3-12 |

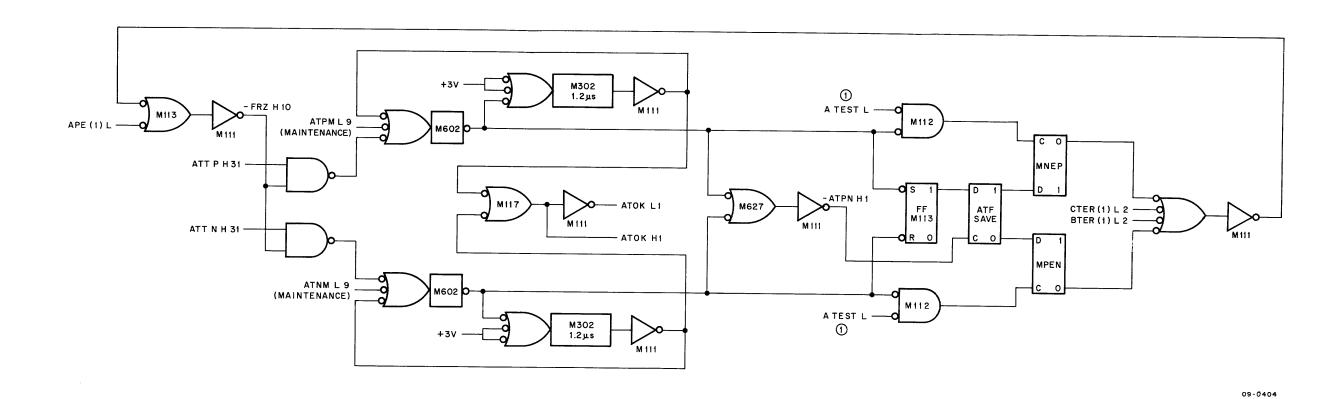

| 4-1        | A Track Error Detection                                  | 09-0404 | 4-3  |

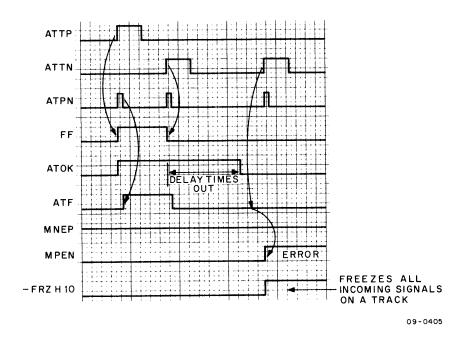

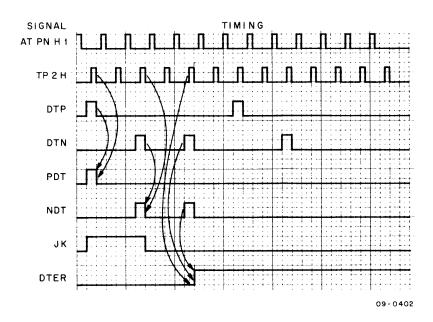

| 4-2        | A Track Error Detection, Timing Diagram                  | 09-0405 | 4-5  |

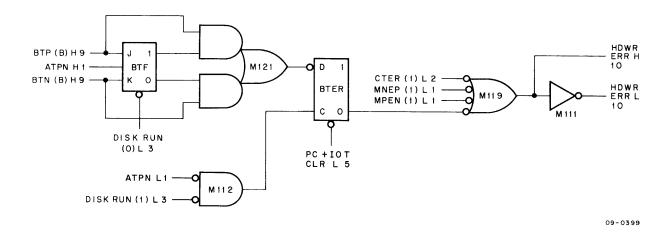

| 4-3        | B Track Error Detection                                  | 09-0399 | 4-5  |

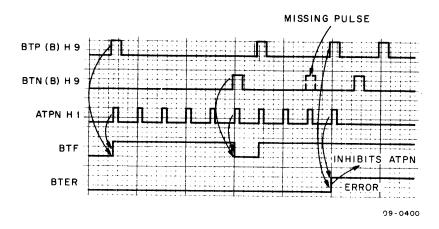

| 4-4        | B Track Timing Diagram                                   | 09-0400 | 4-6  |

| 4-5        | Data Track Error Detection Logic                         | 09-0401 | 4-6  |

| 4-6        | Data Track Timing Diagram                                | 09-0402 | 4-7  |

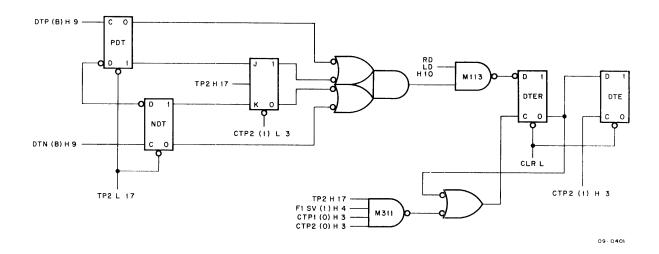

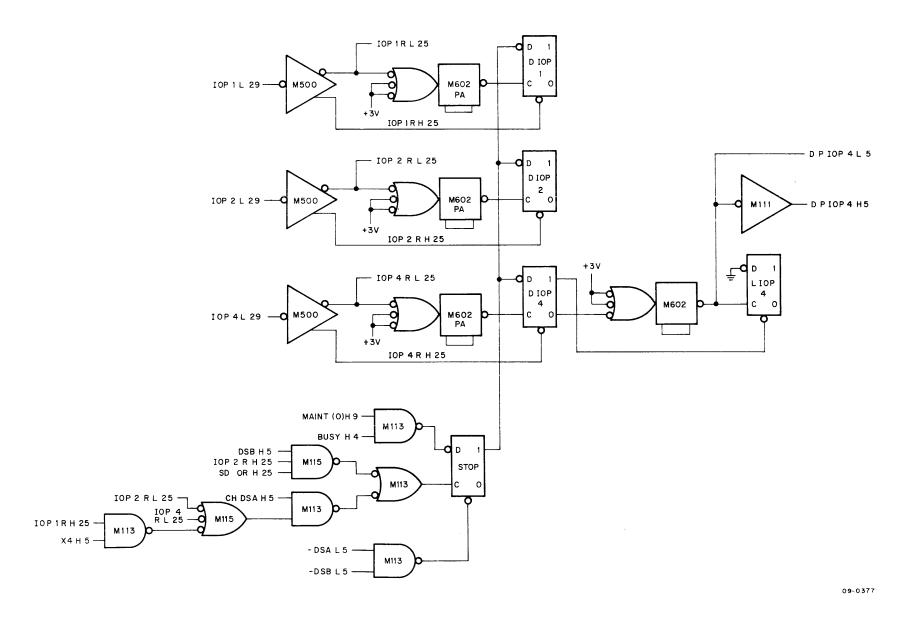

| 4-7        | IOT TRAP Logic                                           | 09-0377 | 4-8  |

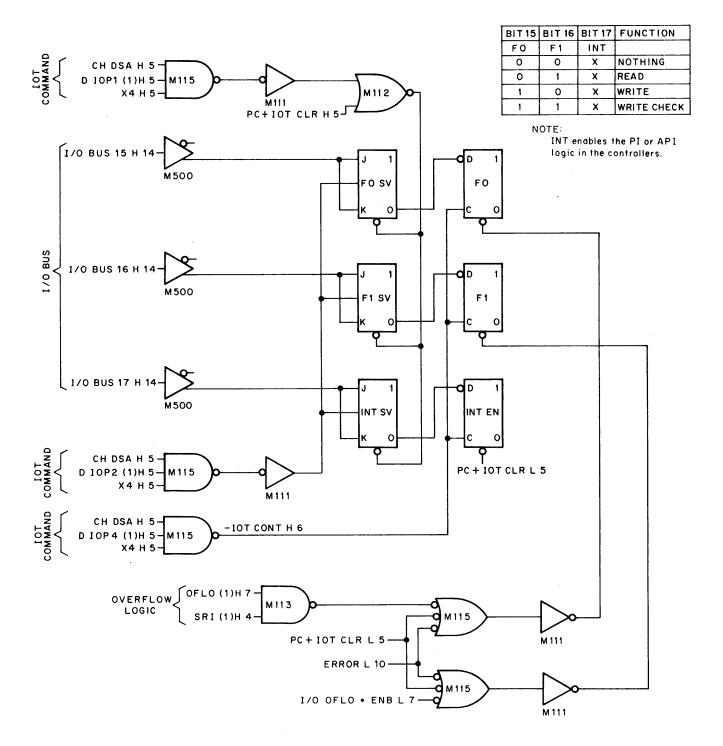

| 4-8        | Function Register                                        | 09-0378 | 4-11 |

| 4-9        | Timing Generator                                         | 09-0396 | 4-13 |

| 4-10       | Timing Generator, Timing Diagram                         | 09-0417 | 4-15 |

| 4-11       | Unlock Sequence Logic                                    | 09-0379 | 4-17 |

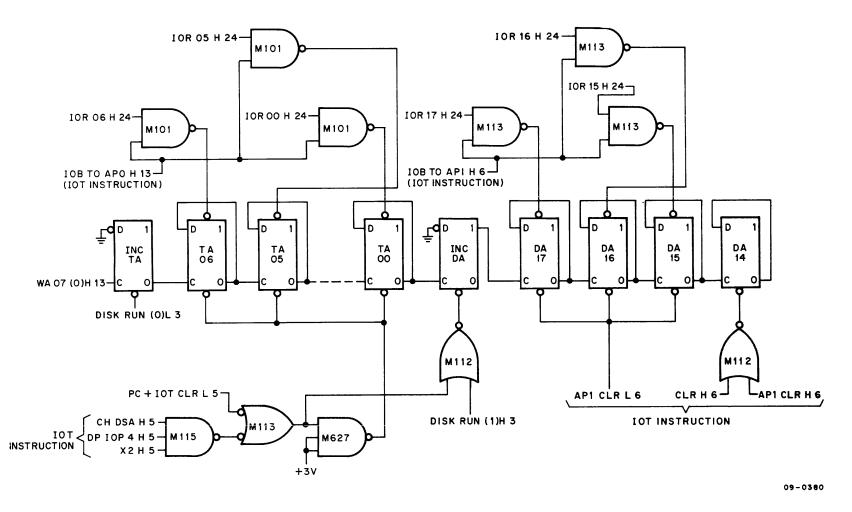

| 4-12       | Track and Disk Address Register                          | 09-0380 | 4-18 |

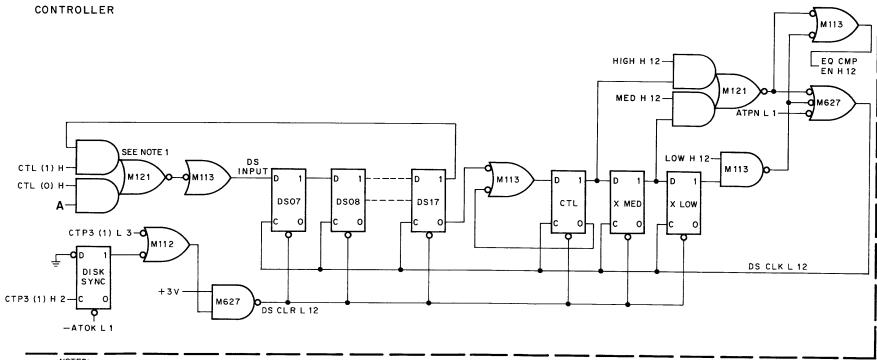

| 4-13       | Disk Segment Register and Transfer Rate Select Logic     | 09-0398 | 4-19 |

| 4-14       | Disk Segment Register, Timing Diagram                    | 09-0146 | 4-21 |

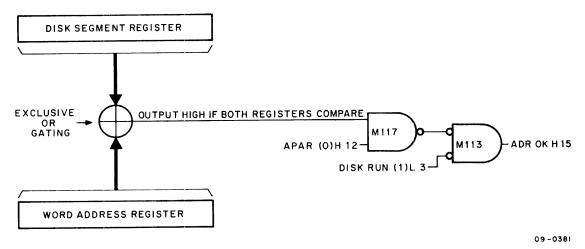

| 4-15       | Equal Comparison Gating                                  | 09-0381 | 4-24 |

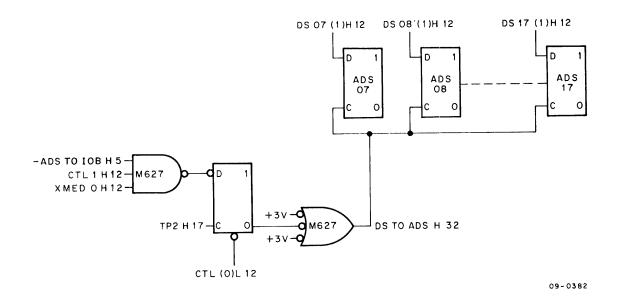

| 4-16       | ADS Register Logic                                       | 09-0382 | 4-24 |

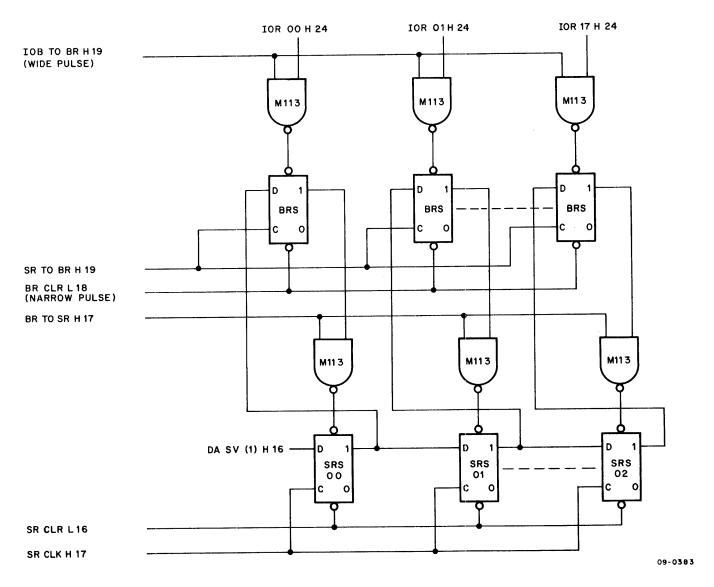

| 4-17       | Buffer Register and Shift Register Interconnections      | 09-0383 | 4-26 |

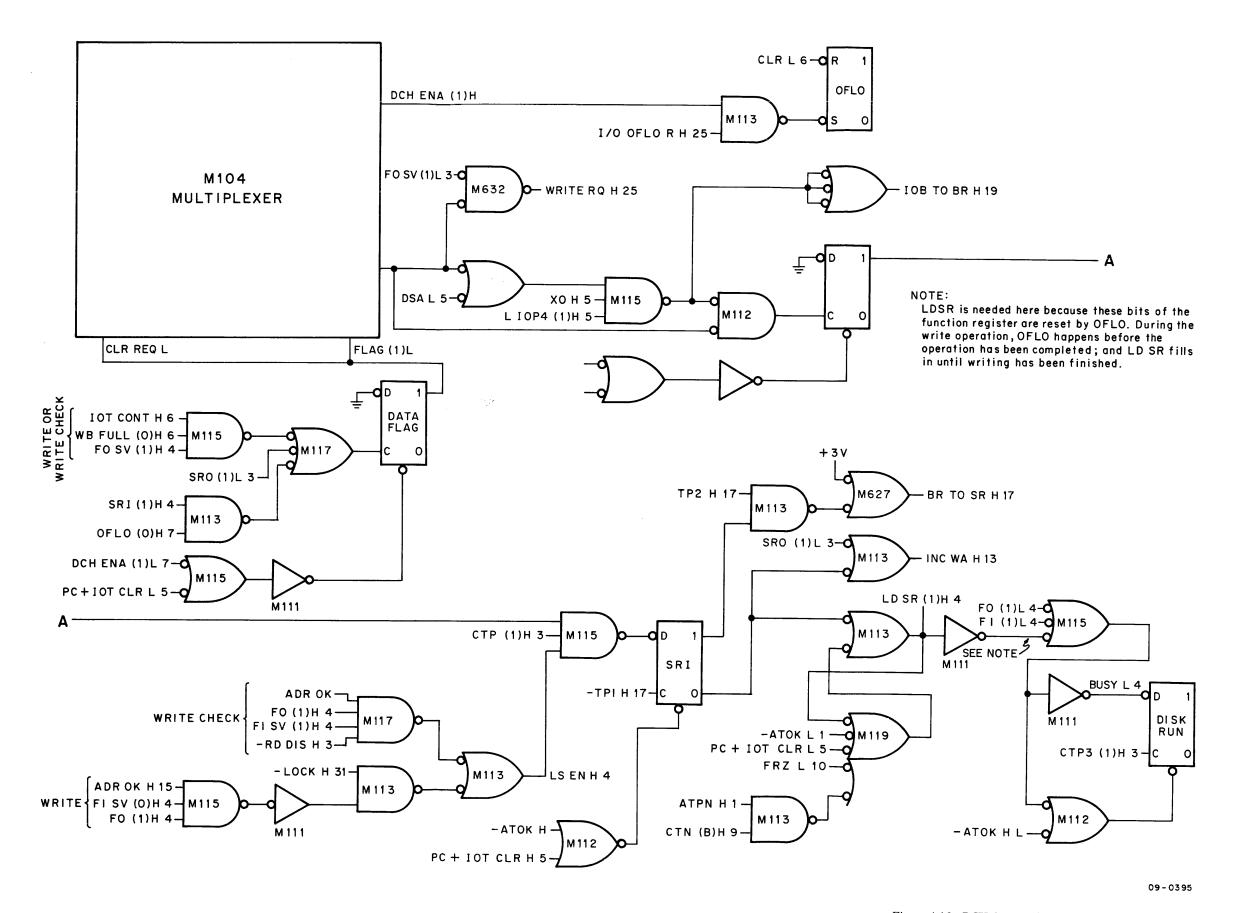

| 4-18       | DCH Control for WRITE and WRITE CHECK                    | 09-0395 | 4-27 |

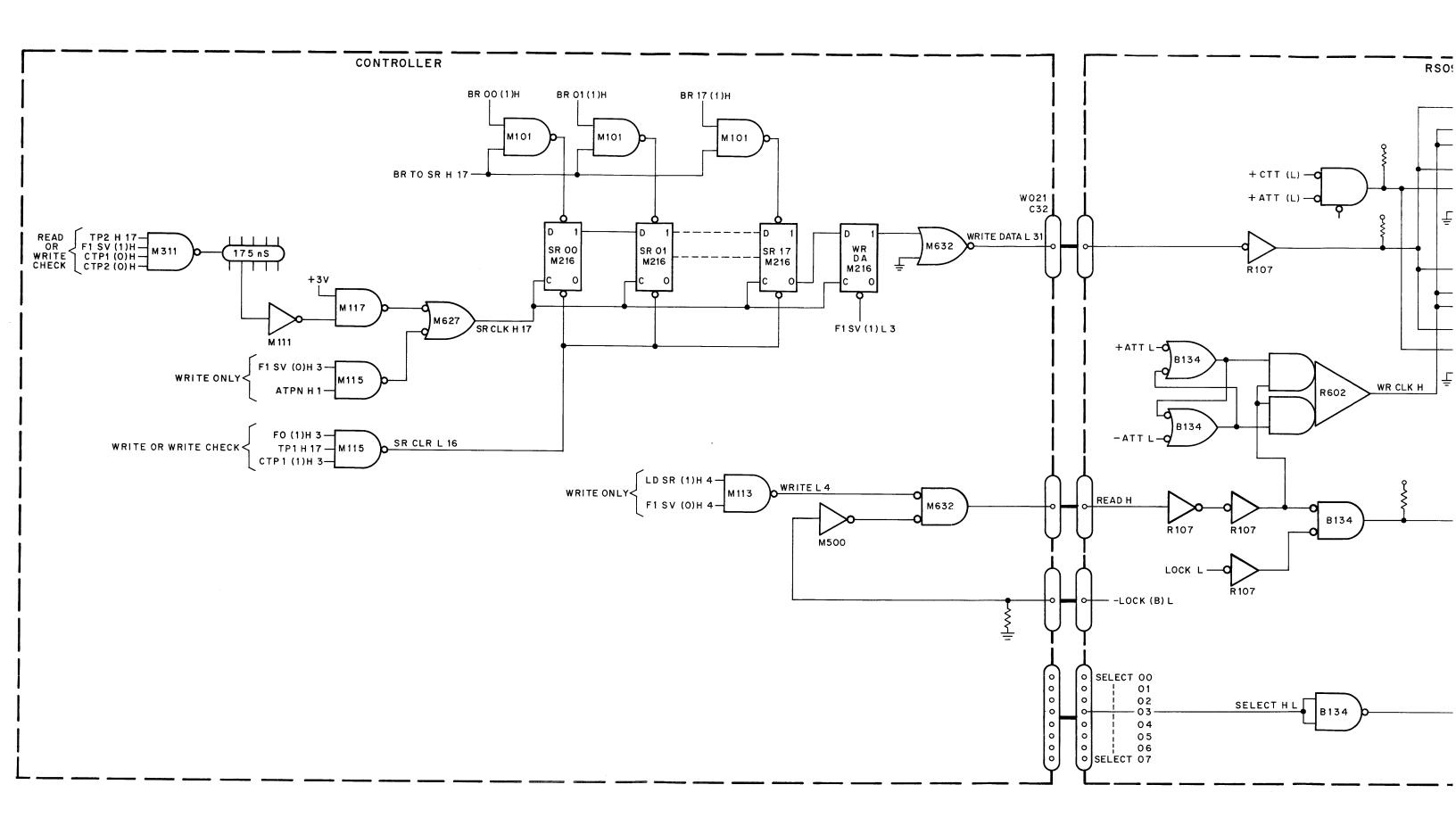

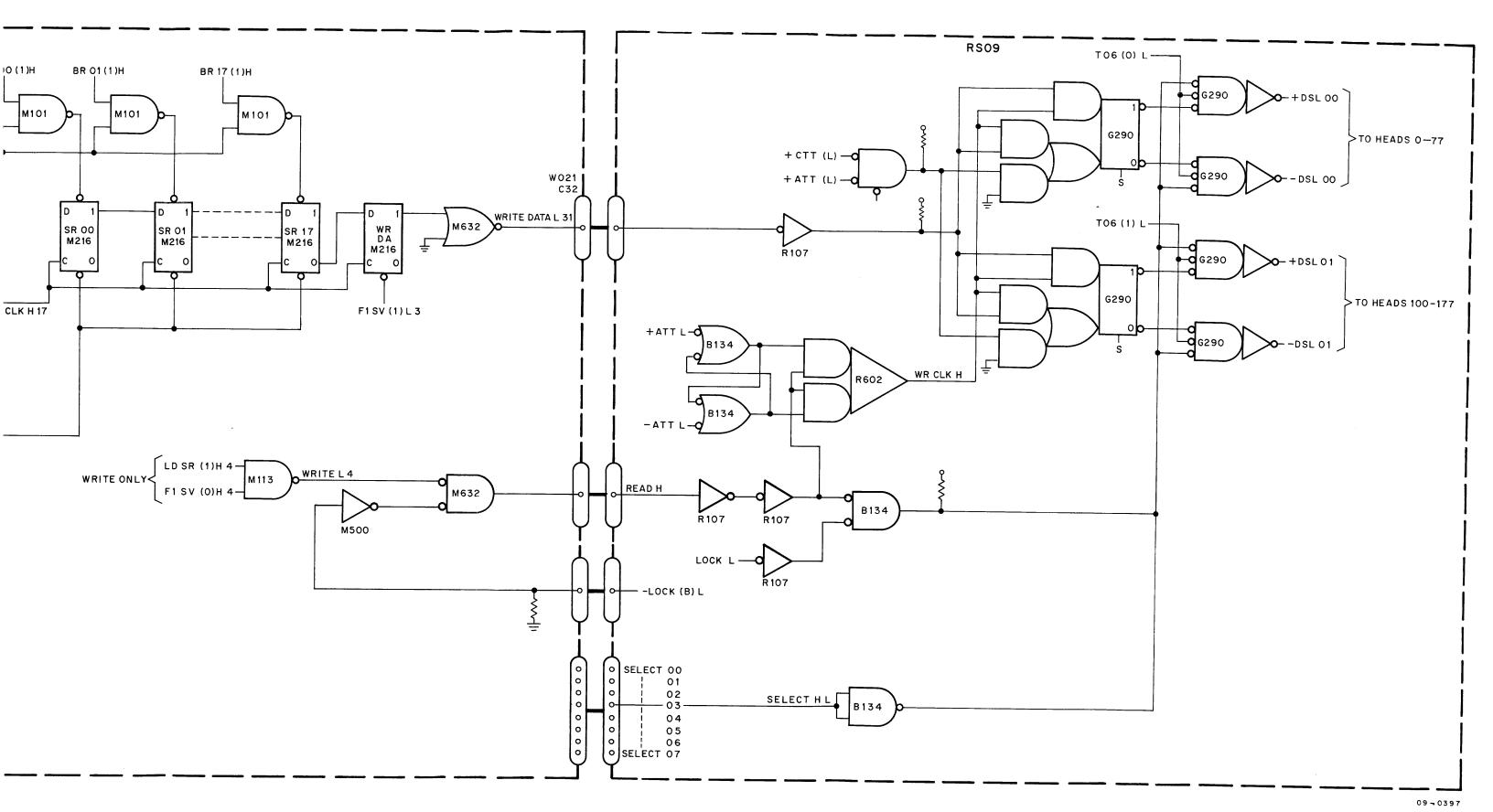

| 4-19       | WRITE Circuitry                                          | 09-0397 | 4-29 |

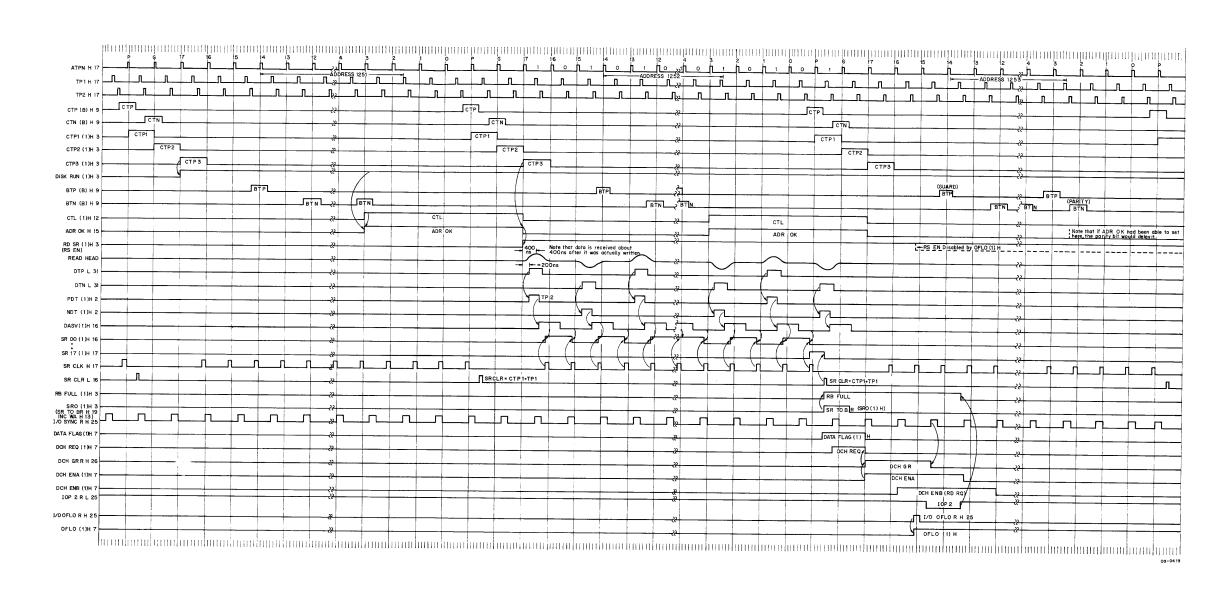

| 4-20       | WRITE Operation for One Word in Address 1251             | 09-0418 | 4-31 |

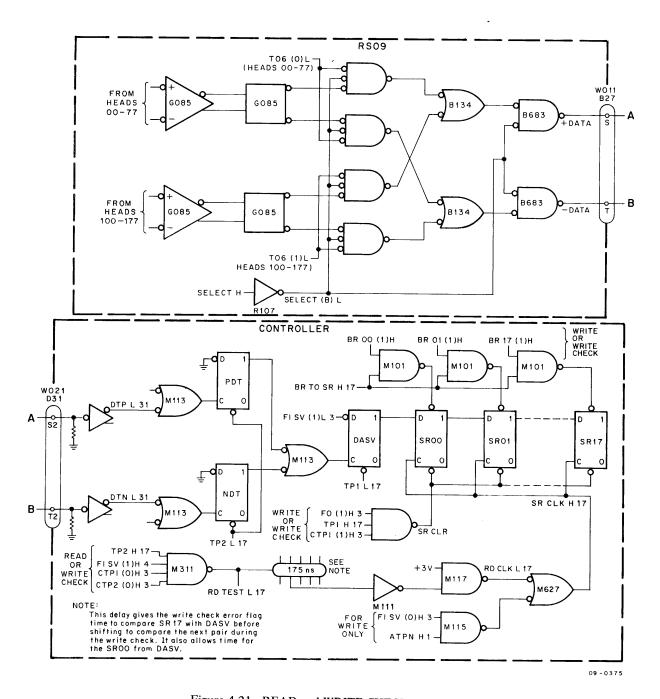

| 4-21       | READ and WRITE CHECK Logic                               | 09-0375 | 4-33 |

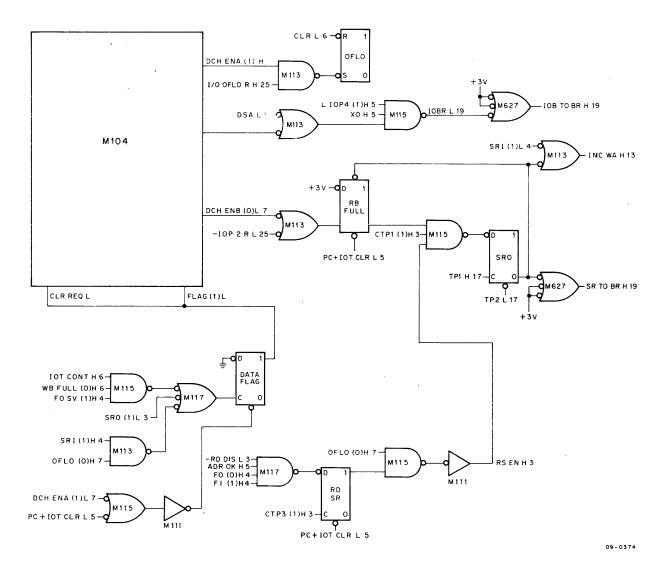

| 4-22       | DCH Control for Read and WRITE CHECK                     | 09-0374 | 4-34 |

| 4-23       | READ Timing Diagram for One Word in Address 1251         | 09-0419 | 4-35 |

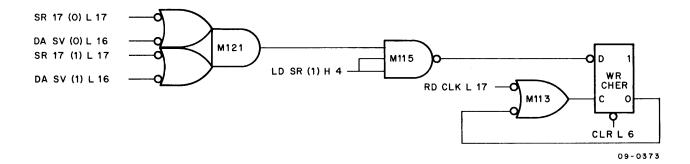

| 4-24       | WRITE CHECK Error                                        | 09-0373 | 4-37 |

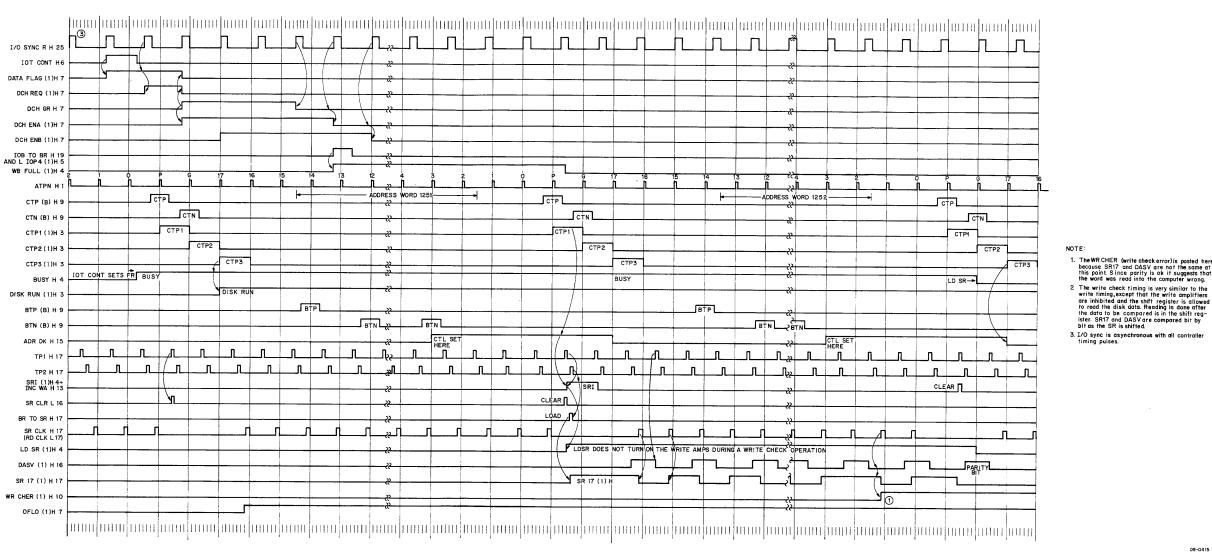

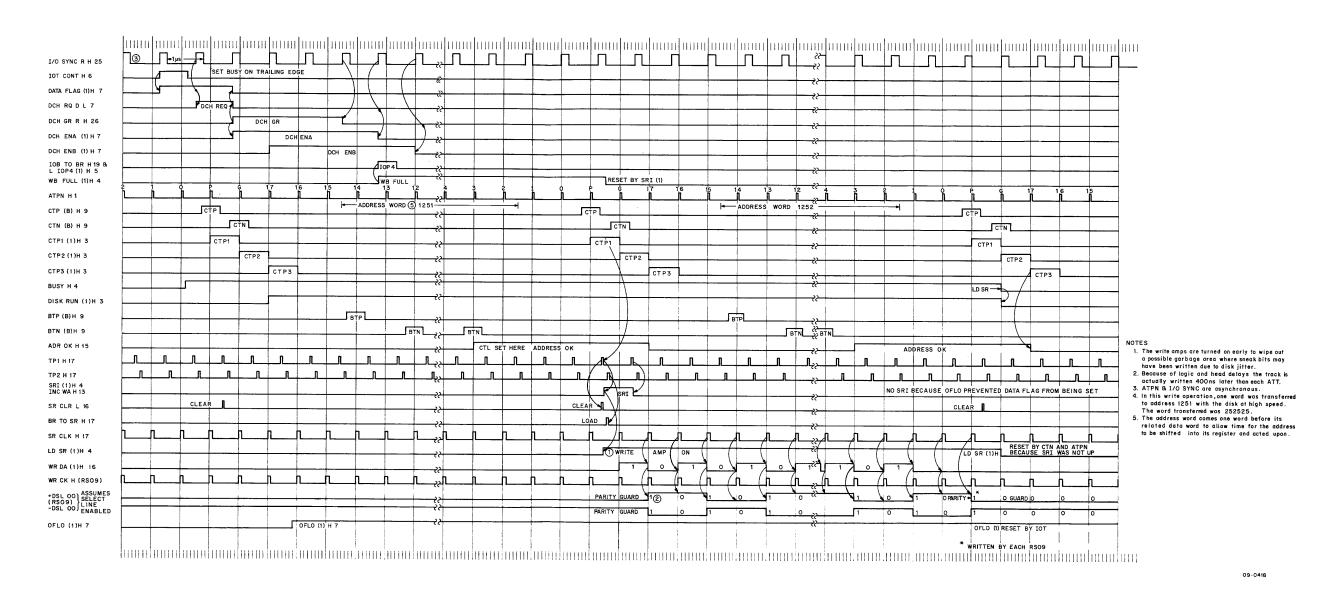

| 4-25       | WRITE CHECK Timing Diagram for One Word in Address 1251  | 09-0415 | 4-39 |

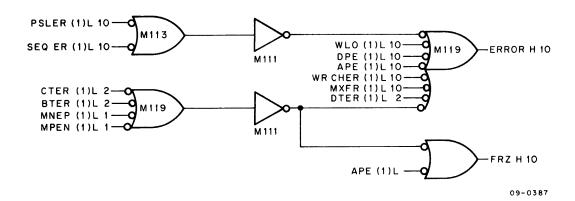

| 4-26       | Error and Freeze                                         | 09-0387 | 4-41 |

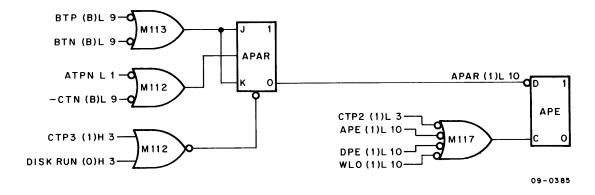

| 4-27       | Address Parity Error                                     | 09-0385 | 4-41 |

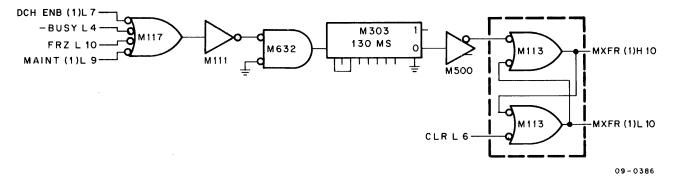

| 4-28       | Missed Transfer Error                                    | 09-0386 | 4-42 |

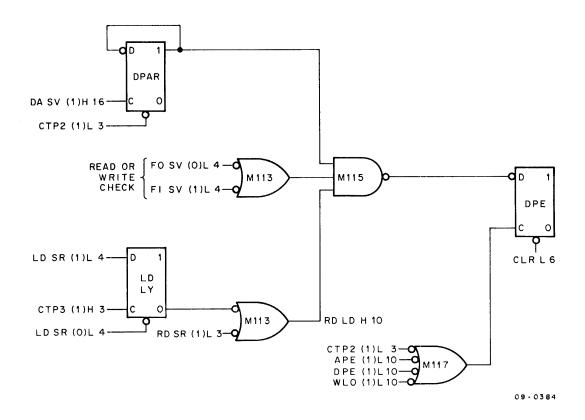

| 4-29       | Data Parity Error                                        | 09-0384 | 4-42 |

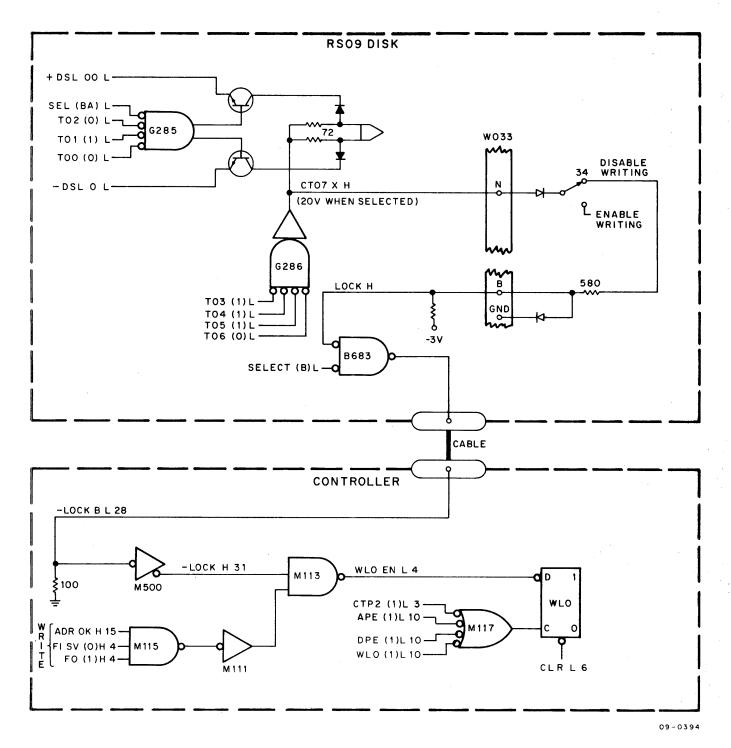

| 4-30       | Write LockOut Error                                      | 09-0934 | 4-43 |

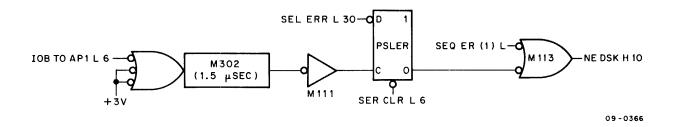

| 4-31       | NonExistent Disk by Program Selector Error               | 09-0366 | 4-44 |

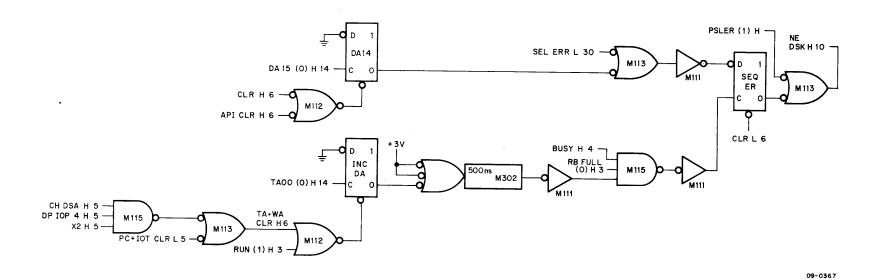

| 4-32       | NonExistent Disk by Sequence Error                       | 09-0367 | 4-45 |

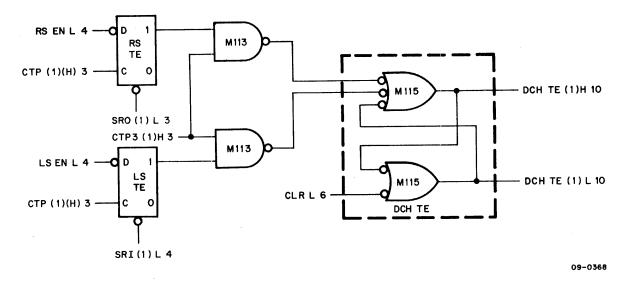

| 4-33       | Data Channel Timing Error                                | 09-0368 | 4-46 |

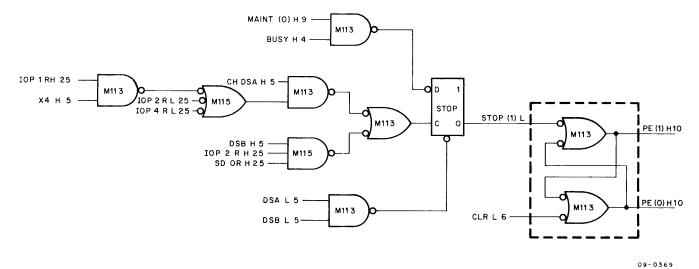

| 4-34       | Program Error                                            | 09-0369 | 4-47 |

| 4-35       | Automatic Priority Interrupt and Program Interrupt Logic | 09-0370 | 4-47 |

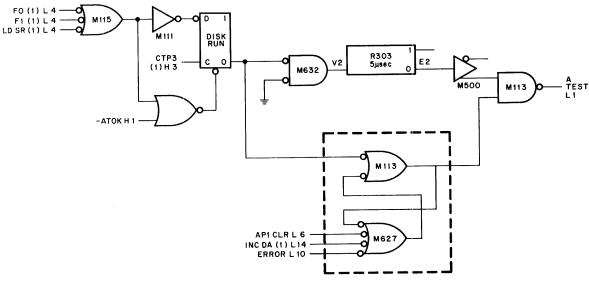

| 4-36       | Disk Run Logic                                           | 09-0371 | 4-48 |

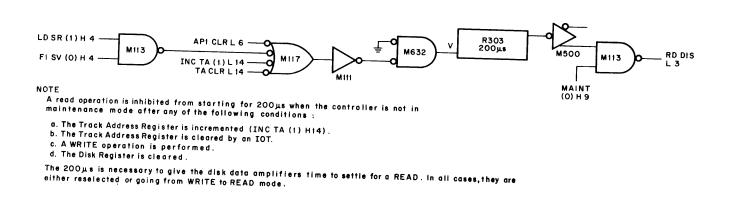

| 4-37       | Read Disable Logic                                       | 09-0372 | 4-49 |

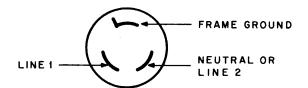

| 5-1        | The RF09 Cabinet                                         | 15-0033 | 5-2  |

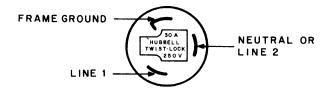

| 5-2        | Hubbell Wall Receptacle Connector Diagram                | 09-0414 | 5-3  |

| 5-3        | Cabinet Bolting Diagram                                  | 15-0098 | 5-5  |

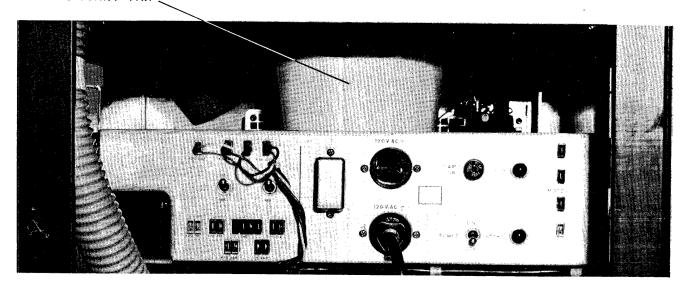

| 5-4        | The RS09 Electronics                                     | 5030-2  | 5-7  |

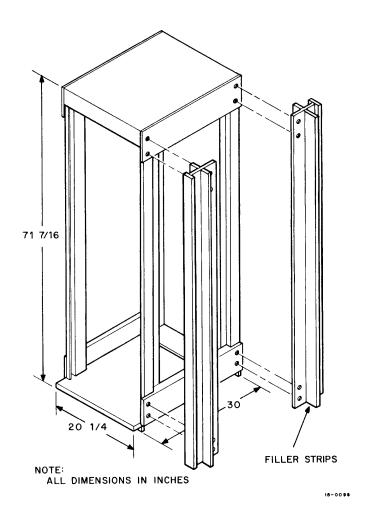

| 5-5        | DECdisk Cabling                                          | 09-0376 | 5-8  |

## ILLUSTRATIONS (Cont)

| Figure No.  | No. Title Art No.                                        |            | Page |

|-------------|----------------------------------------------------------|------------|------|

| 5-6         | The Disk Assembly with Desiccant Pan                     | 5003-14    | 5-9  |

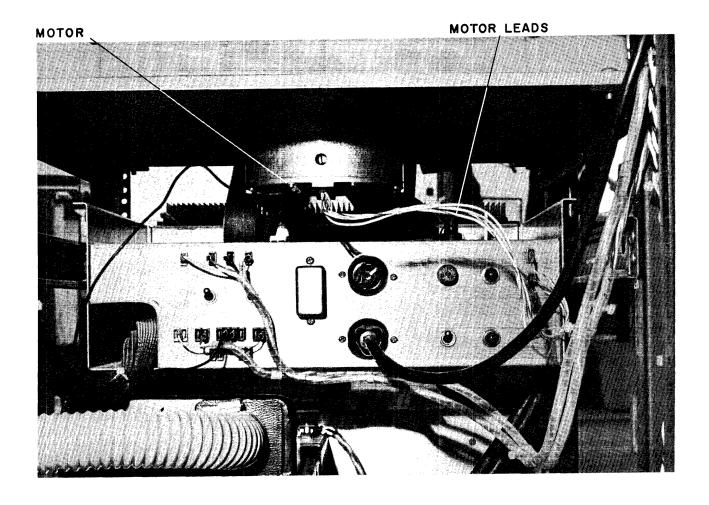

| 5-7         | Disk Assembly with Pan Removed and Motor Leads Connected |            | 5-10 |

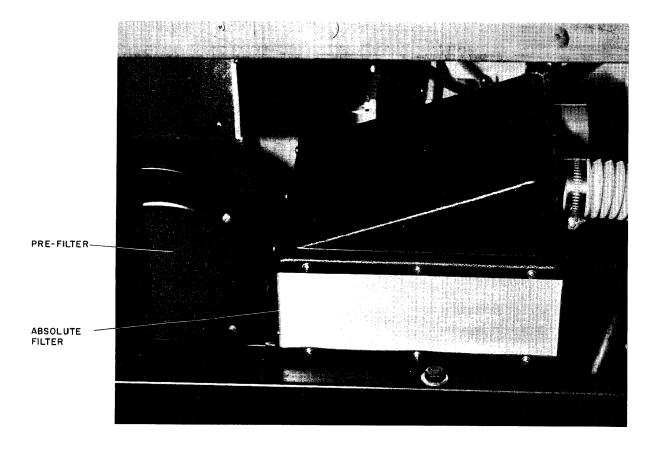

| 6-1         | Purge Unit and Filters 5003-4                            |            | 6-2  |

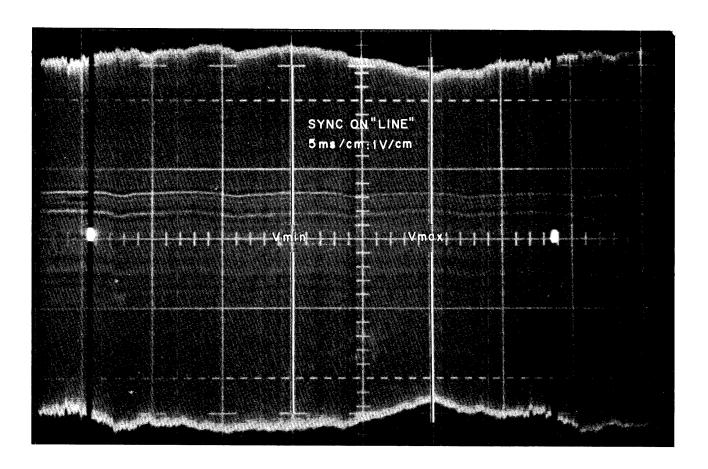

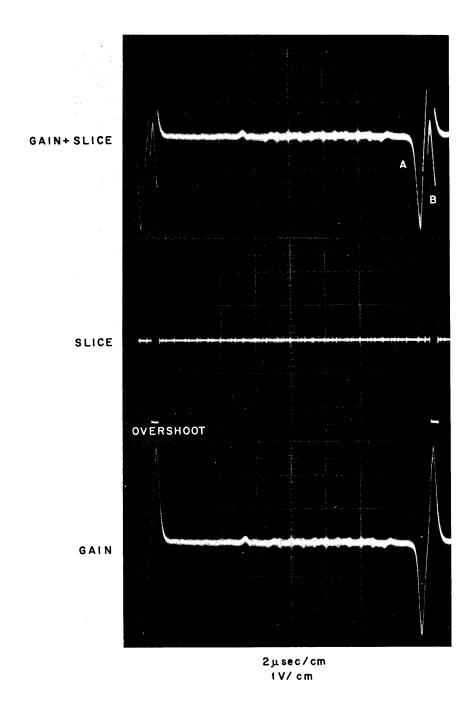

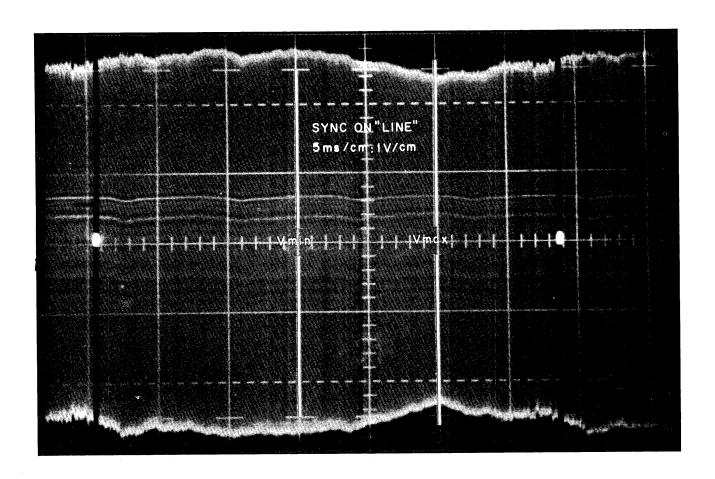

| 6-2         | Measuring Gain, The A Track Over One Revolution          | 5056-1-10A | 6-3  |

| 6-3         | Measuring the Slice of the A Track                       | 09-0403    | 6-5  |

| 6-4         | Measuring the Slice of the B Track                       | 5056-2     | 6-6  |

| 6-5         | Measuring the Slice of the C Track                       | 5056-4     | 6-7  |

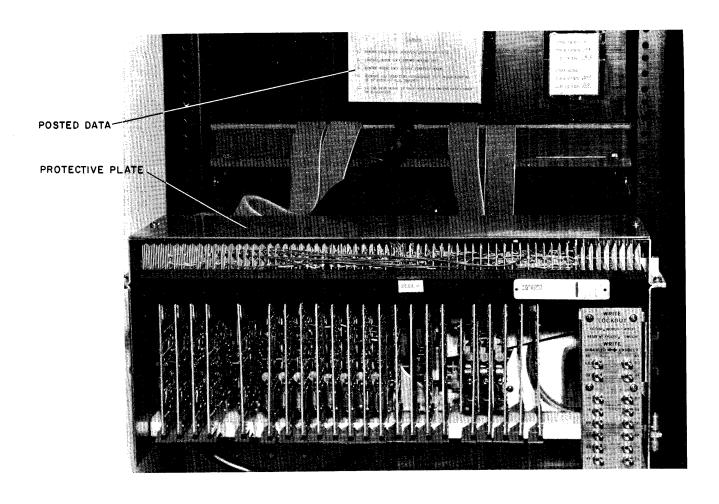

| 6-6         | RS09 Electronics Showing Posted Data                     | 5003-16    | 6-9  |

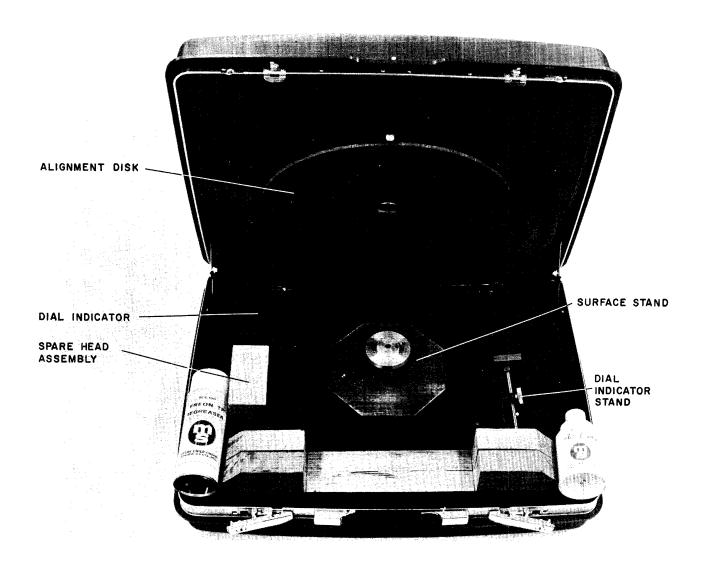

| 7-1         | Disk Assembly Dismantling Kit                            | 5003-11    | 7-4  |

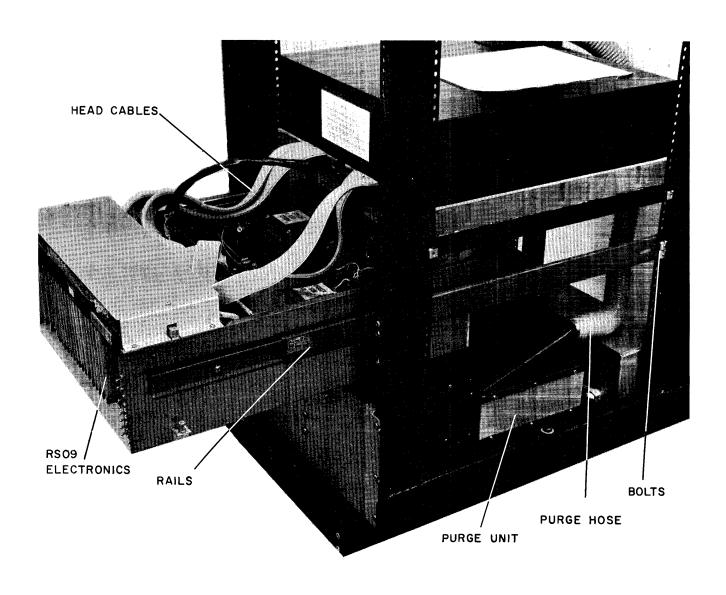

| 7-2         | Removing the Disk Assembly from the Cabinet              | 5003-5     | 7-5  |

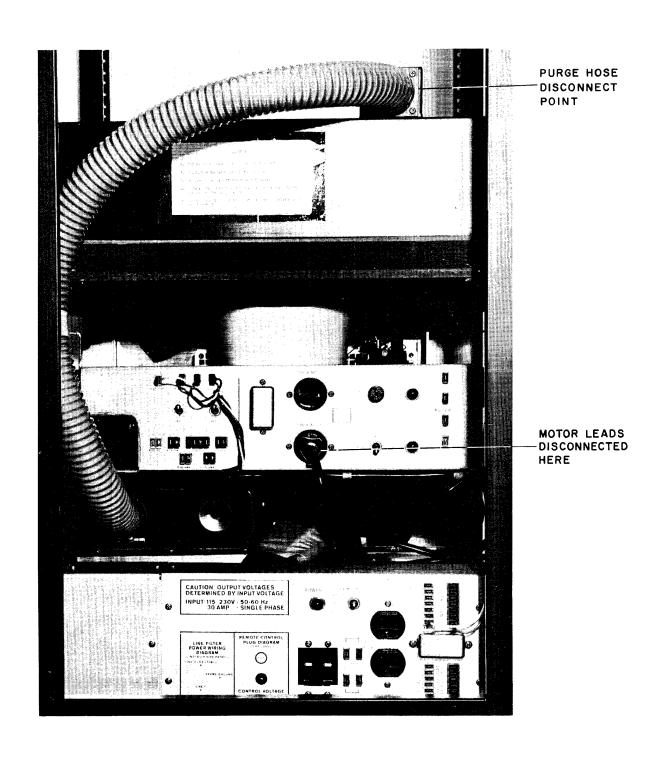

| 7-3         | Disconnecting Motor Leads and Purge Hose                 | 5003-14    | 7-6  |

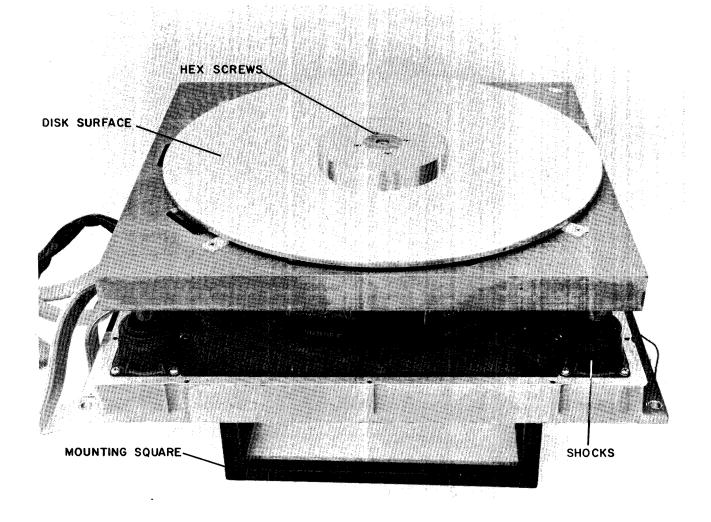

| 7-4         | Disk Assembly With Cover Removed                         | 5003-22    | 7-7  |

| 7-5         | Disk Assembly With Cover and Surface Removed             | 5003-25    | 7-8  |

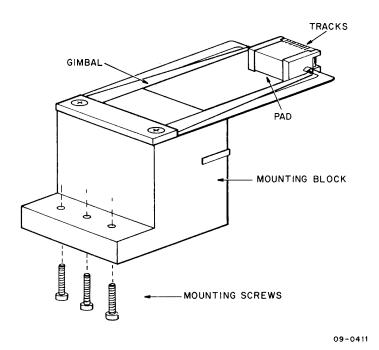

| 7-6         | Shoe Assembly Removed                                    | 5003-10    | 7-9  |

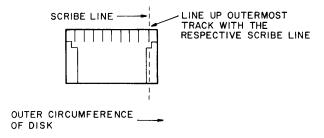

| 7-7         | Aligning the Heads                                       | 09-0411    | 7-11 |

| 7-8         | Aligning the Heads                                       | 09-0412    | 7-12 |

| 7-9         | Timing Track Writer                                      | 5099       | 7-13 |

| 7-10        | Measuring Surface Modulation on the A Track              | 5056-1-10B | 7-15 |

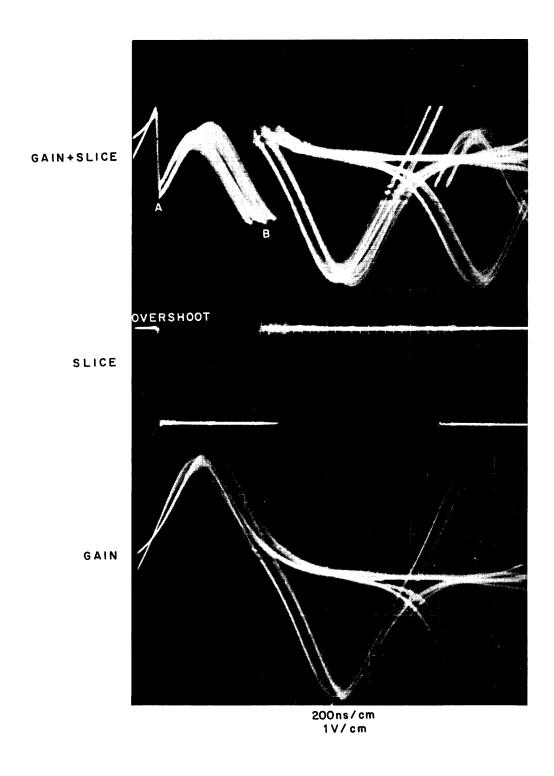

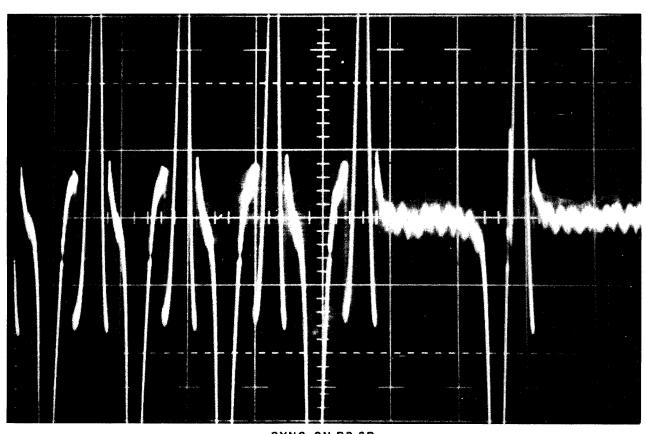

| 7-11        | Maximum Gain, Minimum Slice                              | 5053-3-14  | 7-20 |

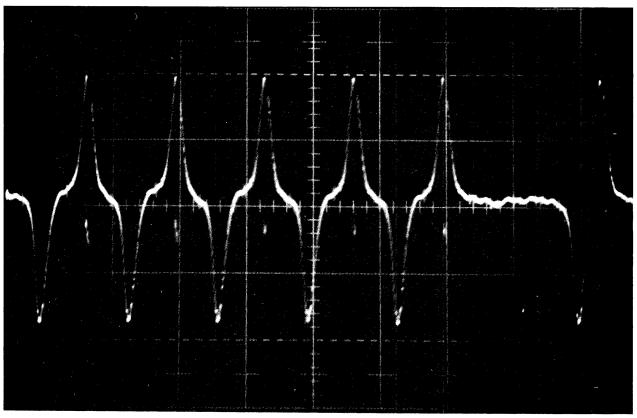

| 7-12        | Minimum Gain, Maximum Slice 5056-3-13                    |            | 7-21 |

| 7-13        | RS09 Test Data Sheet                                     |            | 7-22 |

|             | TABLES                                                   |            |      |

| 1-1         | DECdisk Model Numbers                                    |            | 1-1  |

| 1-2         | The Function Register Bit Configuration                  |            | 1-10 |

| 1-3         | Status Register Bit Functions                            |            | 1-11 |

| 1-4         | The DECdisk Instruction Set                              |            | 1-13 |

| 1-5         | Maintenance IOTs                                         |            | 1-15 |

| 1-6         | The Indicator Panel                                      |            | 1-21 |

| 1-7         | Adjusted ADS Register for Medium and Low Transfer Rates  |            | 1-27 |

| 1-8         | Disk Data Checks                                         |            | 1-29 |

| 4-1         | IOT Decode Effect on Trap Logic                          |            | 4-9  |

| <b>4-</b> 2 | Rotating the Disk Segment Register                       |            | 4-23 |

| 5-1         | Statistics for DECdisk Installations                     |            | 5-2  |

| 6-1         | Visual Inspection Checklist                              |            | 6-1  |

| 7-1         | Setting Up RF09 Delays                                   |            | 7-2  |

| 7-2         | Jumpers to Increase Gain                                 |            | 7-18 |

# Chapter 1 DECdisk System